# Universal Mobility-Field Curves For Electrons In Polysilicon Inversion Layer

M. I. Idris<sup>1</sup>, Faiz Arith<sup>2</sup>, S. A. M. Chachuli<sup>3</sup>, H. H. M. Yusof<sup>4</sup> and M.M. Ismail<sup>5</sup>

<sup>1,2,3,4,5</sup> Faculty of Electronics & Computer Engineering, Universiti Teknikal Malaysia Melaka, Hang Tuah Jaya, 76100 Durian Tunggal, Melaka, Malaysia

Abstract-- This paper reports the studies on the inversion-layer mobility in n-channel Poly-Si TFT's with  $10^{16}$ cm<sup>-3</sup> substrate impurity concentration. The validity and limitations of the universal relationship between the inversion layer mobility and the effective normal field ( $E_{eff}$ ) was examined.

*Index Term*- TFT, Grain boundaries, carrier mobility, polysilicon

## I. INTRODUCTION

It is strongly required to understand the inversion – layer mobility from modeling viewpoint for accurate device simulation, as well as from two-dimensional physics viewpoint. Though a qualitative understanding has already been obtained within moderate device parameters, it is indispensable to establish an accurate mobility model in a wide range of device parameters for realizing future ULSI's. Furthermore, the characterization of mobility degradation is important, in order to predict the performance of Poly-Si TFT's degraded by electric stress and others like trap, de-trap and surface roughness scattering.

On the other hand, it has already been reported that electron and hole mobilities in the inversion-layer follow universal curves, independent of the substrate impurity concentration, when plotted as a function of effective normal field [1]-[3]. This relationship provides a simple guideline, which gives mobility values under a combination of various device parameters.

This paper reports results of mobility behaviors in nchannel Poly-Si TFT's with  $10^{16}$  cm<sup>-3</sup> substrate impurity concentration . Also, the mobility degradation by phonon scattering was studied. From these experimental results, the validity and limitations of the universal relationship have been examined.

## II. SAMPLE PREPARATION AND MEASUREMENT

The n-channel Poly-Si used in this study was fabricated on (100)Si wafer. The substrate impurity concentration is  $10^{16}$ cm<sup>-3</sup> and the gate oxide's thickness is 30nm. The measured devices had 1um gate lengths and 100um

gate widths. The carrier mobility  $\mu_{eff}$  was determined from the drain conductance  $g_D$  for the Poly-Si TFT in the linear region( $V_D = 50$ mV).

$$\mu_{eff} = \frac{L}{W} \cdot \frac{g_D(V_G)}{qN_s(V_G)} \tag{1}$$

Where,

$$E_{eff} = \frac{N_{dpl} + \eta N_s}{\varepsilon_{Si}} \tag{2}$$

and

$$N_{dpl} = \frac{4\varepsilon_{Sl}N_{sub}\phi_b}{q}^{1/2} \tag{3}$$

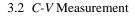

In order to determine  $\mu$ eff accurately, the inversion carrier density  $N_s(V_G)$  must be measured with a minimal measurement error.  $N_s(V_G)$  was therefore ,determined directly through gate-channel capacitance  $C_{gc}(V_G)$  measurement[4-5].

$$qN_s(V_G) = \int_{-\infty}^{V_G} C_{gc}(V_G) dV_G \tag{4}$$

Here, the measurement frequency was 300kHz (depend on the type of device), which enable to measure capacitance values accurately, even near the threshold voltage[5]. The effective normal field ,  $E_{eff}$ , was defined by the following equation.

$$E_{eff} = \frac{q(N_{dpl} + \eta N_s)}{\varepsilon_{si}}$$

(5)

where  $N_{dpl} = (4 \ \varepsilon \ _{Si}Ns_{ub}\varphi_b/q)^{1/2}$  is the bulk surface charge density.  $N_{sub}$  is the substrate impurity concentration, and  $\varphi_b$  is the bulk Fermi energy. Here,  $\eta=1/2$  for electron mobility was used, following previous reports [1]-[3].

# III. EXPERIMENTAL RESULT AND DISCUSSION

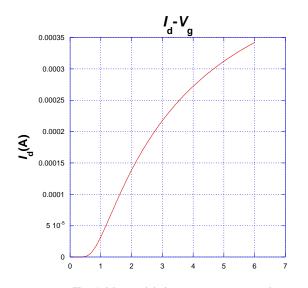

3.1 *I-V* Measurent Result

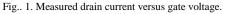

Fig. 2. Measured  $g_m$  versus gate voltage and the way how threshold voltage was determined.

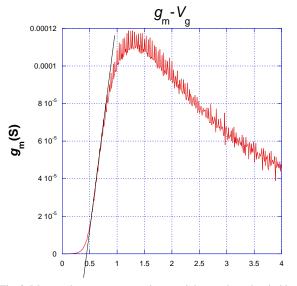

Fig.. 3. Measured drain current versus drain voltage as a parameter of gate voltage.

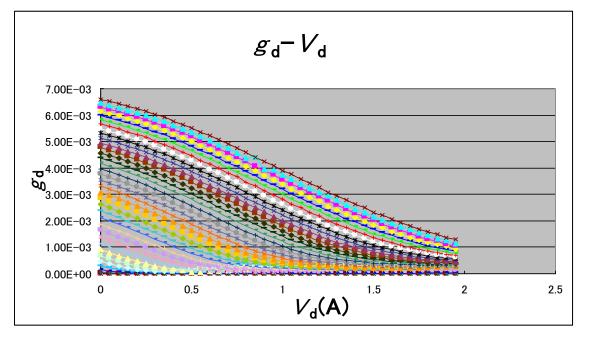

Fig. 4. Measured g<sub>D</sub> versus drain voltage as a parameter of gate voltage.

Fig. 5. Measured gate-capacitance,  $C_{\mbox{\tiny gc}}$  versus gate voltage.

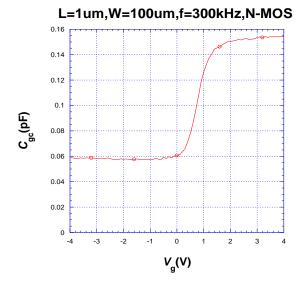

Fig.. 6. Calculated (blue line) and measured (red line) channel charge versus gate voltage is plotted on a linear scale.

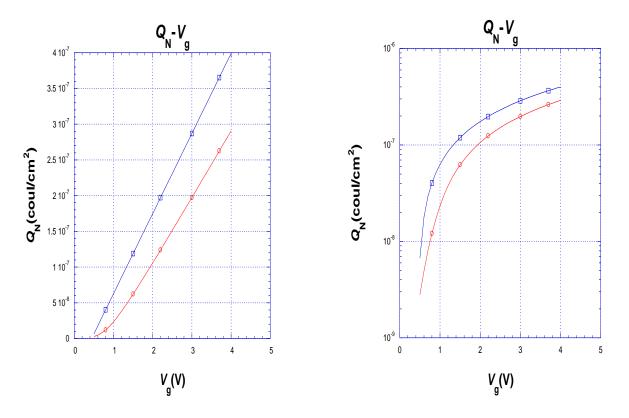

Fig. 7. Calculated (blue line) and measured (red line) channel charge versus gate voltage is plotted on a logarithmic scale.

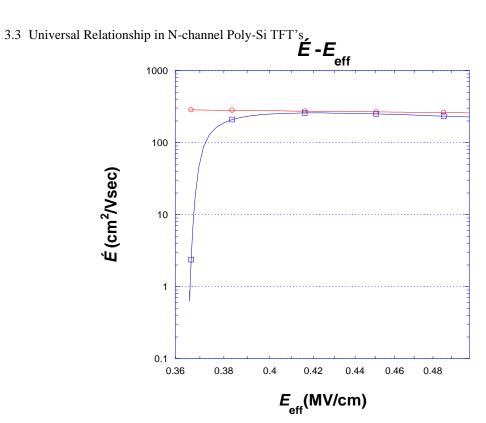

Fig. 8. Effective electron mobility  $\mu_{eff}\,$  in n-channel Poly-Si TFT's versus effective field  $E_{eff.}$

Figure 8 shows the  $E_{eff}$  dependence of the inversion-electron mobility at about 300K(room temperature). It should be notice concerning electron mobility in Figure 8 that the  $E_{eff}$  dependence of electron mobility is in proportion to  $E_{eff}$  <sup>-0.3</sup> at  $E_{eff}$  from 0.4(MV/cm) to 0.45(MV/cm),over the one order of magnitude  $E_{eff}$  range. But electron mobility starts to decrease steeply at  $E_{eff}$  higher than 0.45(MV/cm),though the universality is maintained. Besides, the electron mobility value is degraded to a single figures lower than MOSFET's mobility.

As is well known, the dominant scattering mechanism in the Si inversion-layer is phonon scattering at

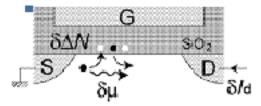

high temperature and surface roughness at low temperature and high normal field. Therefore, it can be considered that the mobility which has  $E_{eff}^{-0.3}$  dependence in figure is limited by phonon scattering [6] and also if  $E_{eff}$  higher than 0.45(MV/cm) the mobility value starts to decrease steeply .Hence , the significant decrease in mobility is thought to be caused by surface roughness scattering[7]. But in Poly-Si TFT, the effect by surface roughness is faster because of the grain- boundaries in channel region. This is also can be explained by electrons trap and de-trap phenomenon(Figure 9).

Fig. 9. Trap and de-trap phenomenon image

### IV. CONCLUSION

This paper reports the studies on the inversion-layer mobility behaviors in n-channel Poly-Si TFT's, from the universal relationship viewpoint. A significant mobility lowering has been observed at low  $N_s$ (low effective field), which is due to Coulomb scattering /screen effect. Also, in n-channel Poly-Si TFT's the significant decrease in mobility is thought to be caused by surface roughness scattering which is faster because of the grain- boundaries in channel region. Besides, the degradation of carrier-mobility in Poly-Si TFT's has been found. This is thought to be caused by grain-boundaries.

From these facts, it can be concluded that, by adding the term of surface roughness and Coulomb scattering to the universal curves, a more accurate description of inversion-layer motilities can be realized.

#### REFERENCES

- A.G.Sabnis and J.TClemens, Charaterization of the electron mobility in the weakly inverted (100)silicon surface, IEDM Technical Digest, p. 18(1979)

- [2] N.D.Arora and G.S.Gildenblat, A semi-empirical model of the MOSFET inversion layer mobility for low temperature operation, IEEE Trans.ED, vol.ED-34,p.89(1987)

- [3] J.T.Watt and J.D.Plummer, Universal mobility-field curves for electrons and holes in MOS inversion layers, Proc.Symp.VLSI Technol., p.81(1987)

- [4] C.G.Sodini, T.WEkstedt and J.L.Moll, Charge accumulation and mobility in thin dielectric MOS transistors, Solid-State Electron, vol. 25, p.833(1982)

- [5] P.D.Chow and K.Wang, A new AC technique for accurate determination of channel charge and mobility in very thin gate MOSFET's, IEEE Trans.ED,vol.ED-33, p.1299(1986)

- [6] S.Kawajiri, The two-dimensional lattice scattering mobility in a semiconductor inversion layer, J.Phys.Soc.Japan., vol.27, p.906(1969)

- [7] Y.C.Cheng and E.A.Sullivan, On the role of scattering by surface roughness in silicon inversion layer, Surf.Sci, vol.34, p.717(1973)