10<sup>th</sup> November 2014. Vol. 69 No.1

© 2005 - 2014 JATIT & LLS. All rights reserved

ISSN: 1992-8645

www.jatit.org

E-ISSN: 1817-3195

# DESIGN AND ANALYSIS OF LOW NOISE AMPLIFIER

# USING CADENCE

# M. I. IDRIS<sup>1</sup>, N. YUSOP<sup>2</sup>, S. A. M. CHACHULI<sup>3</sup>, M.M. ISMAIL<sup>4</sup> FAIZ ARITH<sup>5</sup> AND N. SHAFIE<sup>6</sup>

<sup>1,2,3,4,6</sup> Faculty Of Electronics & Computer Engineering, Universiti Teknikal Malaysia Melaka, Hang Tuah Jaya, 76100 Durian Tunggal, Melaka, Malaysia

E-mail: <u>1idzdihar@utem.edu.my</u>, <u>2norbayah@utem.edu.my</u>, <u>3sitiamaniah@utem.edu.my</u>, <u>4muzafar@utem.edu.my</u>, <u>5faizarith@utem.edu.my</u>, <u>6zayanishafie@gmail.com</u>

## ABSTRACT

Low Noise Amplifier also known as LNA is one of the most significant component for application in wireless communication system. It is a very important part in RF receiver because it can reduce noise of gain by the amplifier when the noise of the amplifier is received directly. The low noise amplifier has been designed to get the better performance by follow the requirement in this new era consists of high gain, low noise figure, lower power consumption, small chip area, low cost and good input and output matching. In this research, a LNA schematic consists of three stages which are common gate amplifier, common drain amplifier and active inductor is designed to mitigate this constraint. Common gate and common drain are used for input and output stages in every LNA. Both are also used for excellent input and output matching and have a potential to get a lower noise whereas for active inductor, it is used to obtain the lower power consumption and to reduce the chip size in layout design. The results show that the proposed LNA is able to achieve the best performance with a simulated gain of 14.7dB, extremely lower power consumption of 0.8mW, noise figure of 7dB and small chip area 0.26mm<sup>2</sup>. Consequently, this modified LNA is appropriate for low-voltage applications especially in wireless communication system.

Keywords: Low Noise Amplifier, inductor, cadence, RF receiver and high gain.

## 1. INTRODUCTION

Low noise amplifier also known as LNA is a special type of electronic that widely used in wireless communication system. A LNA can be found in RF transmitter and receiver for the basic building block in communication system. Hereby, LNA is a very important part of the receiver because it is placed at the front of the receiver and act as an amplifier to amplify the received signals as an electronic amplifier in order to get the level that required with the minimum produced their own additional noise. Basically, radio receiver consists of amplifier, mixer and filter.

Furthermore, the main function of LNA is to amplify a very low signal. This amplification is without adding noise to maintain the required signal to noise ratio at very low power level and for higher signal levels and also the receiver which is receiver sensitivity can be received when the amplification provides the first level. By using this design, the noise can be reduced by the gain and also by the amplifier while the noise of the amplifier is inoculated directly into the received signal.

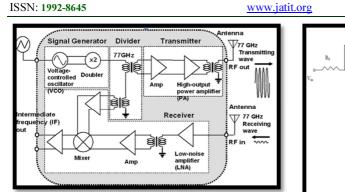

In figure 1, it shows that the basic of RF transmitter and receiver block diagram. It commonly used to modulate and demodulated the transmission of RF signal. The function of the transmitter is to carry the signal whereas the RF receivers receives the signal. Nowadays, the technology has been growing up from time to time and as well as consumer demand requirement that followed the requirement in RF transmitter receivers such as low noise, high gain, low cost, smaller size and good input and output matching. In this proposed project, a design will be created in order to fulfil these requirements.

### Journal of Theoretical and Applied Information Technology 10<sup>th</sup> November 2014. Vol. 69 No.1

© 2005 - 2014 JATIT & LLS. All rights reserved

Figure 1 Block Diagram Of RF Transceiver[1]

## 2. LNA TOPOLOGIES

Low noise amplifier is the first stage in and it is very important part in RF receivers. Hereby, low noise amplifier should be matched with the antenna characteristic. The characteristics of antenna are excellent input and output matching and high gain.

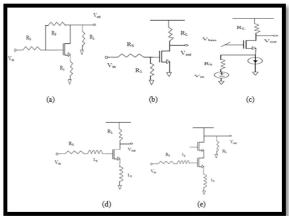

To optimize the low noise amplifier design, the suitable topology should be selected for low power and low voltage. For shunt series feedback common source topology, it is difficult to trade of among gain, small noise figure and good input and output matching with very low power consumption. Meanwhile, for common gate topology, the gain less than 10dB with very low power consumption.

Next, the noise must add to the LNA because of the resistor thermal noise for resistor termination common source topology. Besides that, the specification is satisfied for inductive degeneration common source topology in very low power consumption but the isolation is not good enough compared to the cascade inductor source degeneration topology which can get the similar low noise amplifier performance with very low power consumption. Lastly, for cascade inductor source degeneration topology provides higher gain with a low noise figure.[2]

Hence, there are several fundamental types of topologies for low noise amplifier and a common low noise amplifier has been choosen for optimizing the LNA design. Figure 2 shows the toplogies of LNA:

E-ISSN: 1817-3195

# 3. METHODOLOGY

In this design there are mainly three stages in the proposed LNA. Every stage is explained in greater detail in Figure 3.

Figure 3 Block Diaram Of Three Stages LNA[3]

1. Common Gate Amplifier

Basically, common gate amplifier is widely used in electronic field and one of three basic single stages field-effect transistor (FET) topologies. The advantages by using this FET are:

- i. Used as current buffer or voltage amplifier.

- ii. Used as input stage for LNA

- Obtain input impedance matching. The input impedance depends only on the trans-conductance of CMOS shown in equation 1.

$$Zin = \frac{1}{gm}$$

iv. Potentially has lower noise

<u>10<sup>th</sup> November 2014. Vol. 69 No.1</u> © 2005 - 2014 JATIT & LLS. All rights reserved

|                    | ő                | 3/111             |

|--------------------|------------------|-------------------|

| ISSN: 1992-8645    | www.jatit.org    | E-ISSN: 1817-3195 |

| 2. Active Inductor | Cgs3(1 + Rfgds4) |                   |

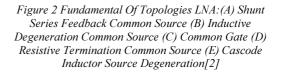

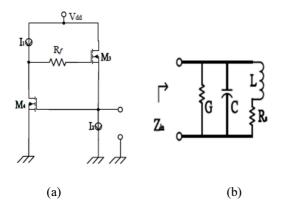

The active inductor has been implemented in this design which performs the same function as passive inductors. Active inductor is a combination of CMOS transistors. To design a low noise amplifier it has a fewer difficulty but it has higher flexibility to get the input and output matching, easy to design the layout and it does not have the magnetic field. For this design it does not used the real active inductor as main function but change it with transistor that perform the same function with active inductor. The advantages by using active inductor are:

- i. To get lower power consumption.

- ii. Used to reduce chip area

- iii. Used to reduce complexity

- iv. Used to reduce cost

- v. Used to compensate for the affect of parasitic capacitors at high frequencies

Figure 4 Active Inductor Circuit And His Equivalent Circuit[3]

In figure 4(a) and (b), the quality factor (Q) inductance (L), and frequency (w) is calculated from the equation below:[3]

$$Q \approx \sqrt{\frac{\text{gm4gm3Cgs3} \times (1 + \text{Rfgds4})}{\text{gds4}^2\text{Cgs4}}}$$

This quality factor is high enough because it depends on Rf.

$$L \approx \frac{\text{Cgs3}(1 + \text{Rfgds4})}{\text{gm4gm3}}$$

$$w = \frac{\text{gm4gm3}}{\text{Cgs4Cgs3}(1 + \text{Rfgds4})}$$

After the design is implemented with the equivalent circuit, it has been improved by using double feedback with second order. Figure 5 shows the active inductor after the improvement.

Figure 5 Double Feedback With Second Order Circuits[3]

#### 3. Common drain amplifier

Common drain amplifier is one of three basic single-stages (FET) amplifier topologies also known as a source follower. It is usually used as a voltage buffer. The advantages by using this FET are:

- i. Used as a final stage in every LNA

- ii. Capable to get small output

- impedance matching iii. Potentially has lower noise

#### 4. LITERATURE REVIEW

Based on the literature review, the comparisons of low noise amplifier design have been made to choose the appropriate schematic circuit for this project. From the comparison in Table 3, the first journal, Hamzeh Fatehi, 2013, that have been chosen because of the best performance in term of the parameters that have been compared which are technology, gain (db), frequency (Ghz), noise figure (db), power supply, power consumption and area/ die size[4]. Table 1 shows the comparison of the LNA design as below:

<u>10<sup>th</sup> November 2014. Vol. 69 No.1</u>

© 2005 - 2014 JATIT & LLS. All rights reserved

| ISSN: 1992-8645 | www.jatit.org | E-ISSN: 1817-3195 |

|-----------------|---------------|-------------------|

|-----------------|---------------|-------------------|

Table 1 Comparison Of The LNA Design

(We are unable to place the figure here due to its size which is placed at the endof the manuscript)

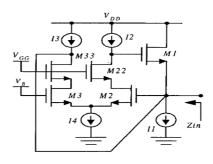

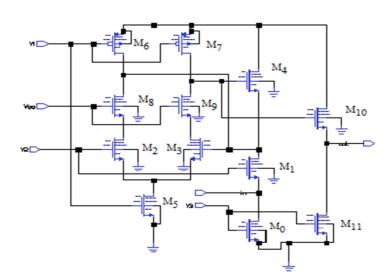

## 4.1 Proposed A Low Noise Amplifier Circuit

From the comparison the proposed a low noise amplifier circuit has been selected based on the best performance in term of the noise figure, high gain and power consumption. The proposed low noise amplifier circuit uses the active inductor to achieve the requirements. In addition, it is implemented with latest CMOS technology  $0.13\mu m$ .

(We are unable to place the figure here due to its size which is placed at the below of the manuscript)

Figure 6 Schematic Of Proposed Low Noise Amplifier[3]

#### 4.2 Enhancement Circuit

This circuit will be modified from the researcher Hamzeh Fatehi. This design will enhance with the change of CMOS technology from  $0.18 \mu m$  to  $0.13 \mu m$ . Furthermore, the transistor size also will be change.

| Transistor | Width  |

|------------|--------|

| M0         | 8 um   |

| M1,M2,M3   | 12 um  |

| M4,M5      | 1.8 um |

| M6,M7      | 2 um   |

| M8,M9      | 4 um   |

| M10        | 3.6 um |

| M11        | 2.7 um |

Table 2 Transistor Width [3]

# 4.3 Design Specification Of LNA

There are some important specifications that LNA should achieve. The specifications of LNA design are indicated in Table 3

Table 3 Specifications Of LNA Design[6]

| Parameter            | Specification |

|----------------------|---------------|

| Supply Voltage       | 1.8V          |

| Gain                 | >10dB         |

| Noise Figure         | <3dB          |

| Power<br>Consumption | <50mW         |

| DC current           | <20mA         |

#### 5. DISCUSSION AND RESULTS

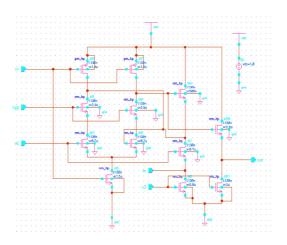

Design and analysis of low noise amplifier is designed and simulated by using CADENCE software with latest technology  $0.13\mu m$ . The DC biasing voltage values for this design are V1= 1.1, V2=0.6, V3=0.6 and Vgg=0.7 respectively.

In this new design the ratios (W/L) of the transistor that used in this circuit have been fixed. For the transistor lengths the value are  $0.13\mu$ m for all transistors while the transistor width the value are different by using the manual calculation. Figure 7 shows the schematic circuit of the proposed LNA design and Table 4 shows the transistor ratio after the enhancement.

Figure 7 Schematic Of Proposed Low Noise Amplifier After Enhancement

Table 4: Size Transistor After Enhancement

#### Journal of Theoretical and Applied Information Technology 10<sup>th</sup> November 2014. Vol. 69 No.1 © 2005 - 2014 JATIT & LLS. All rights reserved. ISSN: 1992-8645 E-ISSN: 1817-3195 www.jatit.org Transistor Width Length M0 5.8um 0.13um M1,M2,M3 8.7um 0.13um M4 0.5um 0.13um M5 1.3um 0.13um M6,M7 1.4um 0.13um M8,M9 2.9um 0.13um M10 2.6um 0.13um M11 2um 0.13um

#### Figure 9 Gain In Positive Value

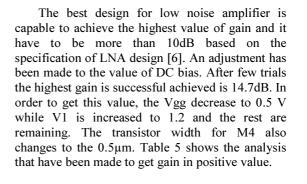

## 5.1 Major Challenging

While completing the design, there are major challenges arise of producing the right value of gain. On the first experiment, all the transistors are combined into one ground nodes. The result shows that, gain value is negative. So, it does not meet the requirement of gain which it must be in positive value. Then it proceeds to second experiment. The ground nodes are connected to each transistor respectively. Based on these experiments, it can be concluded that the ground nodes cannot be combined because of the input DC biasing value for each transistor is different. Figure 8 and 9 show the gain in negative value and positive value.

Table 5 Analysis Of Gain Value

Figure 8 Gain In Negative Value

| Vgg | V1  | V2  | V3  | Gain(dB) |

|-----|-----|-----|-----|----------|

| 0.5 | 1.2 | 0.6 | 0.6 | 11.39    |

| 0.7 | 1.1 | 0.6 | 0.6 | 9.22     |

| 0.4 | 1.1 | 0.6 | 0.6 | -23.9    |

| 0.5 | 1   | 0.6 | 0.6 | -30.63   |

| 0.5 | 1.3 | 0.6 | 0.6 | 10.9     |

| 0.5 | 1.4 | 0.6 | 0.6 | 11.86    |

| 0.5 | 1.5 | 0.6 | 0.6 | 11.56    |

| 0.5 | 1.5 | 0.7 | 0.6 | 4        |

| 0.5 | 1.5 | 0.5 | 0.6 | 7.753    |

| 0.5 | 1.5 | 0.5 | 0.7 | 4.48     |

| 0.5 | 1.5 | 0.5 | 0.5 | -31      |

| 0.4 | 12  | 07  | 0.6 | -2       |

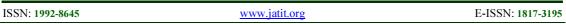

### 5.2 Transient Analysis

The transient analysis is very important to the amplifier. It is because from this analysis it can proved that this design is an amplifier or not. The function of the amplifier is to amplify the output signal from the input signal. Therefore, to prove that this design is an amplifierm the output signal

10<sup>th</sup> November 2014. Vol. 69 No.1

© 2005 - 2014 JATIT & LLS. All rights reserved

must greater than the input signal. Figure 10 shows **5.4 Summary Of Simulation Result** the simulation result of transient analysis.

Figure 10 Transient Analysis Simulation

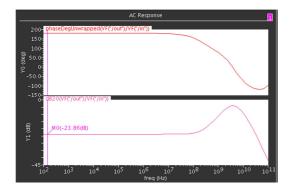

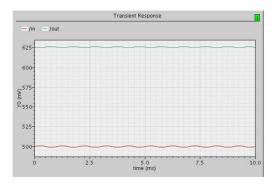

# 5.3 AC Analysis Result

After transient analysis is done, the AC analysis for LNA design is obtained. To achieve the desired specifications gain, optimum transistor width, input value of DC biasing voltage was the main criteria for design of LNA[15,16]. When high gain has been achieved the noise can be reduce by gain of the amplifier that captured by antenna. To obtain the gain of the LNA design, below expression can be used[17]:

$$Gain = 20\log_{10}(\frac{Vout}{Vin})$$

For this design the gain is successfully achieved with 14.7dB based on the design specification. Figure 11 shows the simulation result of gain in AC analysis

Figure 11 AC Analysis Simulation

The overall of the specification of LNA design

| were met.   | The simulation | results | are | shown | in | th |

|-------------|----------------|---------|-----|-------|----|----|

| Table 6 bel | ow:            |         |     |       |    |    |

|             |                |         |     |       |    |    |

Table 6 Simulation Result

| Parameter            | Specification | Simulation Result |

|----------------------|---------------|-------------------|

| Supply Voltage       | 1.8V          | 1.8V              |

| Gain                 | >10dB         | 14.7dB            |

| Noise Figure         | <3dB          | 7dB               |

| Power<br>Consumption | <50mW         | 0.8mW             |

| DC current           | <20mA         | 0.45mA            |

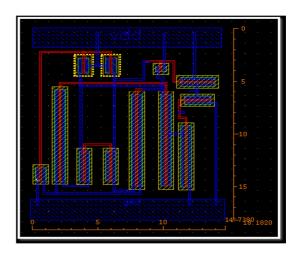

# 5.5 Layout Design

In figure 12, the layout of low noise amplifier is designed by using CADENCE software with  $0.13\mu m$  CMOS technology. The parameters of transistor width are followed as in Table 4. It also shows the smallest chip area which is  $0.26 mm^2$ .

Figure 12 Layout Design Of LNA

| © 2005 - 2014 JATIT &                                                                                                                                                                                                                                                                                                                                                                                              |               |                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISSN: 1992-8645 www.jat                                                                                                                                                                                                                                                                                                                                                                                            | <u>it.org</u> | E-ISSN: 1817-3195                                                                                                                                                                                                                                               |

| 5.6 Comparison With Other Published Work                                                                                                                                                                                                                                                                                                                                                                           |               | Systems Engineering, UKM, ISSN 1392-<br>1215,Vol.19, NO.5,2013.                                                                                                                                                                                                 |

| Table 7 shows the summary of proposed LNA design simulation result and comparison with other published work.                                                                                                                                                                                                                                                                                                       | [4]           | N. Moser, S. J. Rogers, P. Supervisor, and<br>J. Rogers, "ELEC 4907 – Fourth Year<br>Engineering Project Final Report A 5.2                                                                                                                                     |

| (We are unable to place the figure here due to its size which is placed at the below of the manuscript)                                                                                                                                                                                                                                                                                                            |               | GHz Differential Cascode Low Noise Amplifier," 2004.                                                                                                                                                                                                            |

| Table 7 Comparison With Other Works                                                                                                                                                                                                                                                                                                                                                                                | [5]           | P. Version, "Low Noise Amplifier Design<br>Measuremants," Inc.,555 Riber                                                                                                                                                                                        |

| 6. CONCLUSION                                                                                                                                                                                                                                                                                                                                                                                                      |               | Oaksparkway, San Jose, CA 9514, USA,,<br>Product Version 5.0, September 2004.                                                                                                                                                                                   |

| An improved design of low noise amplifier using<br>active inductor is presented in this research. The<br>modified circuit has bee design by using the<br>CADENCE 0.13um CMOS technology. The<br>objective of this design was accomplished based on<br>the specifications of the LNA. According to the<br>resesearch result, the circuit is capable to achieve<br>gain of 14.7dB, noise of 7dB, extremely low power | [6]           | N.Rani, S.Sharma, "Design of Low Noise<br>Amplifier at 3-10GHz for Ultra Wideband<br>Receiver,"international Journal of<br>Innovation Research in Computer and<br>Communication Engineering, Vol.1, Issue<br>7, September 2013.                                 |

| gain of 14.7dB, holse of 7dB, extremely low power<br>consumption of 0.8mW, good input and output<br>matching. However it has the problem with the<br>noise due to the usage of the latest technology<br>which is 0.13 $\mu$ m. it is designed by using<br>CADENCE software with latest technology<br>0.13 $\mu$ m. Lastly, the circuit size reduced<br>significantly to small chip size of 0.26mm <sup>2</sup> .   | [7]           | P. Kavyashree and S. S. Yellampalli, "The<br>Design of Low Noise Amplifiers in<br>Nanometer Technology for WiMAX<br>Applications," M.Tech(VLSI Design),<br>VTU Extension Centre, UTL Technologies<br>Limited Bangalore, India,vol. 3, no. 10, pp.<br>1–6, 2013. |

| ACKNOWLEDGEMENTS<br>The authors would like to thank to University                                                                                                                                                                                                                                                                                                                                                  | [8]           | P. G. Afshar, "International Journal of<br>Advanced Research in A 3 . 5 GHz Low<br>Noise Figure Mixer with High Conversion                                                                                                                                      |

Teknikal Malaysia Melaka (UTeM) and Ministry of Higher Education for the support, facilities and financial support throughout the project.

## **REFERENCES:**

- J. Brown, "Design of a Magnetically Tunable Low Noise Amplifier in 0.13 um CMOS, "(2012). Graduate Thesis and Dissertations, Paper 12672.

- [2] S. Kumar, "CMOS Low Noise RF Amplifier Design and Parameter Estimation using ANN,"Master of Technology in VLSI Design &CAD vol. 147004, 2012.

- [3] H. Aljarajreh, M. B. I. Reaz, M. S. Amin, and H. Husain, "An Active Inductor Based Low Noise Amplifier for RF Receive," Department of Electrical, Electronic and

- [9] B. Liu, C. Wang, M. Ma, and S. Guo, "An Ultra-Low-Voltage and Ultra-Low-Power," School of Computer and Communication, Hunan University, China vol. 18, no. 4, pp. 527–531, 2009.

695-699, 2013.

Gain for WiMAX Systems," IEEE of

Advanced Research in Computtr Science

and Software Engineering, vol. 3, no. 5, pp.

- [10] A. Goel and G. Singh, "A Novel Low Noise High Gain CMOS Instrumentation Amplifier for Biomedical Applications," Centre for Development of Advanced Computing (C-DAC), Mohal, India, vol. 3, no. 4, pp. 516–523, 2013.

- [11] C. George and J. Rogers, "Design of Broadband Low Noise Amplifier for use in

|       | <u>10<sup>th</sup> November 2</u><br>© 2005 - 2014 JATIT &                                                                                                                                                                                                                                                       |       |                                                                                                                                                                                                                                                   |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISSN: | 1992-8645 <u>www.jati</u>                                                                                                                                                                                                                                                                                        | t.org | E-ISSN: 1817-3195                                                                                                                                                                                                                                 |

| [12]  | <ul><li>a Cable Tuner.," Final project Report., vol. 51, no. 2, p. Contents2, Jan. 2014.</li><li>E. D. Link, "CMOS LNA Design for Multi-Standard Aplication," Master Thesis at Electronic Devices Linkopings Institute of Technology, 2006.</li></ul>                                                            | [19]  | P. Jha and P. Vishwakarma, "Design of RF<br>Front-End Low Noise Amplifier for an<br>Ultra Wideband Receiver," Electronics<br>&Communication Department,NIET<br>Greater Noida, India,Journal of Electron<br>Devices, Vol. 13, pp. 1006–1011, 2012. |

| [13]  | SS. Kim, YS. Lee, and TY. Yun,<br>"High-Gain Wideband CMOS Low Noise<br>Amplifier with Two-Stage Cascode and<br>Simplified Chebyshev Filter," <i>ETRI J.</i> , vol.<br>29, no. 5, pp. 670–672, Oct. 2007.                                                                                                        | [20]  | <ul> <li>T. Thi and T. Nga, "Ultra low-power low-noise amplifier designs for 2 . 4 GHz ISM band applications," School of Electrical &amp; Electronic Engineering no. July, 2012.</li> <li>G.Nohra,"Low Voltage CMOS Low Noise</li> </ul>          |

| [14]  | R. R. Harrison, C. Charles, and S. Member,<br>"A Low-Power Low-Noise CMOS<br>Amplifier for Neural Recording<br>Applications," IEEE Journal of Solid-State<br>Circuits vol. 38, no. 6, pp. 958–965, June<br>2003.                                                                                                 |       | Amplifier Design."A Thesis in Department<br>of Electrical and Computer Engineering,<br>Cancordia University Montreal,Quebec<br>Canada, August 2005.                                                                                               |

| [15]  | M. Idzdihar Idris, M.N. Shah Zainuddin, M.<br>Muzafar Ismail, R. Abd. Rahim, "Design of<br>a Low Voltage Class AB Variable Gain<br>Amplifier (VGA)", Journal of<br>Telecomunication, Electronic and<br>Computer Engineering(JTEC),Vol.4 No.2,<br>ISSN:2180-1843, pp. 69-74, 2012.                                |       |                                                                                                                                                                                                                                                   |

| [16]  | Idris, M. I. B., Reaz, M. B. I., Bhuiyan, M.<br>A. S., A Low Voltage VGA For RFID<br>Technology", Receivers, 2013 IEEE<br>International Conference on RFID-<br>Technologies and Applications, (2013), 1-4                                                                                                        |       |                                                                                                                                                                                                                                                   |

| [17]  | Mohammad Arif Sobhan BHUIYAN,<br>Muhammad Idzdihar Bin IDRIS, Mamun<br>Bin Ibne REAZ, Khairun Nisa MINHAD,<br>Hafizah HUSAIN "Low Voltage and Wide<br>Bandwidth Class AB Variable Gain<br>Amplifier in 0.18-µm CMOS Technology",<br>PRZEGLĄD ELEKTROTECHNICZNY,<br>ISSN 0033-2097, R. 90 NR 6/2014, 184-<br>187. |       |                                                                                                                                                                                                                                                   |

| [18]  | J. Brown, "Design of a Magnetically<br>Tunable Low Noise Amplifier in 0 . 13 um<br>CMOS Technology," 2012.                                                                                                                                                                                                       |       |                                                                                                                                                                                                                                                   |

© 2005 - 2014 JATIT & LLS. All rights reserved

ISSN: 1992-8645

www.jatit.org Table 1 Comparison Of The Lna Design

|      | Technology | Gain (dB) | Frequency (GHz) | Noise<br>Figure (dB) | Power<br>supply | Power<br>consumption | Area/die size |

|------|------------|-----------|-----------------|----------------------|-----------------|----------------------|---------------|

| [3]  | CMOS 0.18  | 20        | 2-3             | 3.1                  | 1.8             | 0.5                  | 0.003         |

| [5]  | CMOS 0.18  | 15.04     | 8.72            | 3.85                 | 1.8             | 4.7                  | -             |

| [6]  | CMOS 0.18  | 17.04     | 5.8             | 3.1                  | 1.8             | 6.4                  | -             |

|      | CMOS 0.18  | 15.7      | 5.9             | 1.85                 | 1               | 19.3                 | -             |

| [7]  |            | 19.9      | 5.9             | 2.63                 | 1               | 56.8                 | -             |

| [8]  | CMOS 0.18  | 1.2       | 3.5             | 6.5                  | 1.5             | 10.12                | -             |

| [9]  | CMOS 0.18  | 14.3      | 2.4             | 1.6                  | 1.8             | 0.9                  | -             |

| [10] | CMOS 0.18  | 67.7      | -               | -                    | -               | -                    | -             |

| [4]  | CMOS 0.18  | 19.5      | 5.2             | 2.7                  | 3               | -                    | -             |

| [11] | CMOS 0.18  | 12-14     | -               | -                    | 5.5-6           | -                    | -             |

| [12] | CMOS 0.18  | -         | 2.4             | 2.17                 | -               | -                    | -             |

| [13] | CMOS 0.18  | -         | 8.2             | 3.3-6.3              | -               | 17.3                 | -             |

| [14] | -          | 39.8      | -               | -                    | 2.5             | -                    | 0.2           |

Figure 6 Schematic Of Proposed Low Noise Amplifier[3]

# Journal of Theoretical and Applied Information Technology 10<sup>th</sup> November 2014. Vol. 69 No.1

© 2005 - 2014 JATIT & LLS. All rights reserved

ISSN: 1992-8645

www.jatit.org

E-ISSN: 1817-3195

Table 7 Comparison With Other Works

|           | Technology | Gain (dB) | Noise Figure | Power  | Power consumption | Area/die size |

|-----------|------------|-----------|--------------|--------|-------------------|---------------|

|           | (µm)       | Gain (ub) | (dB)         | supply | (mW)              | (mm²)         |

| This work | CMOS 0.13  | 14.7      | 7            | 1.8    | 0.8               | 0.26          |

| [18]      | CMOS 0.13  | 16.2      | 7.5          | -      | 50                | -             |

| [19]      | CMOS 0.13  | 16.2      | 1.76-1.96    | -      | -                 | -             |

| [20]      | CMOS 0.13  | 14        | 3.55         | 1.8    | 1.13              | -             |

| [21]      | CMOS 0.13  | 5.3       | 1.8          | 1.5    | 11                | -             |