# **Faculty of Electrical Engineering**

# A COMPARATIVE STUDY OF DIODE-CLAMPED AND CASCADED H-BRIDGE IN MULTILEVEL INVERTER FOR HARMONIC REDUCTION

**Mohammed Rasheed Jubair**

**Master of Electrical Engineering**

(Industrial power)

2014

C Universiti Teknikal Malaysia Melaka

# A COMPARATIVE STUDY OF DIODE-CLAMPED AND CASCADED H-BRIDGE IN MULTILEVEL INVERTER FOR HARMONIC REDUCTION

### MOHAMMED RASHEED JUBAIR

A dissertation submitted In partial fulfilment of the requirements for the degree of Master of Electrical Engineering (Industrial power)

**Faculty of Electrical Engineering**

## UNIVERSITI TEKNIKAL MALAYSIA MELAKA

2014

C Universiti Teknikal Malaysia Melaka

### DECLARATION

I declare that this dissertation entitled "Comparative Study Of Diode-Clamped and Cascaded H-Bridge Multilevel Inverter for Harmonic Reduction" is the result of my own research except as cited in the references. The dissertation has not been accepted for any degree and is not concurrently submitted in the candidature of any other degree.

Signature

fer

Name

: Mohammed Rasheed Jubair Date : 02/08/2014

i.

### APPROVAL

I hereby declare that I have read this dissertation and in my opinion, this dissertation is a sufficient term of the scope and quality of the award of master of electrical engineering (Industrial Power).

Signature ROSLI BIN OMAR PROF. MADY TIMBALA DEKAN (PENYELIDIKAN & PENGAJIAN SISWAZAH) Supervisor Name Fakulti Kejuruteraan Elektrik hikal Malaysia Melaka Universiti Tel Date 2

ii

### ABSTRACT

This dissertation presents a comparative study of two types of multilevel inverters that comprise of diode clamped and cascaded H-Bridge multilevel inverter for reduction of harmonics in the multilevel inverter output. The proposed system is designed using MATLAB/SIMULINK and it consists of diode clamped and cascaded H-Bridge multilevel inverters. The controller is based on the pulse width modulation (PWM) technique which is applied to the purposed three phase multilevel inverters. The various performances of simulation results of the diode clamped and cascaded H-Bridge multilevel inverters were investigated. The Total harmonic distortion (THDv) of the output voltage was measured for the two types of multilevel inverters. Based on varying simulation results, it has been found that the THD voltage of the H-Bridge multilevel inverter is considerably lower than the diode clamped multilevel inverter.

iii

### ABSTRAK

Disertasi ini membentangkan satu kajian perbandingan dua jenis penyongsang pelbagai peringkat, terdiri daripada diod diapit dan disebarkan H-Bridge penyongsang bertingkat untuk mengurangkan harmonik dalam output penyongsang pelbagai peringkat. Sistem yang dicadangkan ini direka menggunakan MATLAB / SIMULINK dan ia terdiri daripada diod diapit dan disebarkan H-Bridge penyongsang pelbagai peringkat. Pengawal ini adalah berdasarkan modulasi lebar denyut (PWM) teknik yang digunakan untuk berniatlah tiga fasa penyongsang pelbagai peringkat. Pelbagai persembahan daripada keputusan simulasi diod diapit dan disebarkan H-Bridge penyongsang bertingkat telah disiasat. Jumlah herotan harmonik (THDv) voltan keluaran diukur untuk kedua-dua jenis penyongsang pelbagai peringkat. Berdasarkan berbeza keputusan simulasi, didapati bahawa voltan THD daripada H-Bridge penyongsang bertingkat adalah jauh lebih rendah daripada diod diapit penyongsang pelbagai peringkat.

iv

#### ACKNOWLEDGMENTS

First and foremost, Alhamdulillah, I thank to Allah the Almighty for his blessings. 1 would like to take this opportunity to express my sincere acknowledgement to my supervisor Associate Professor Ir. Dr. Rosli Omar from the Faculty of Electrical Engineering, Universiti Teknikal Malaysia Melaka (UTeM) for her essential supervision, support and encouragement towards the completion of this dissertation.

My appreciation goes to my family and all my close friends who are as close as family, they have been a constant source of encouragement and love. Of course, most of all I must thank my parents for their absolute support, love, and above all patience.

v

## DEDICATION

I dedicate this message to my father and my mother particularly cherished. Without their support and most of all love, the completion of the hard work \ was not possible.

### TABLE OF CONTENT

| DI | ECLA  | RATION                                                              | 1      |

|----|-------|---------------------------------------------------------------------|--------|

| AF | PRO   | VAL                                                                 | ü      |

| AF | BSTRA | ACT                                                                 | 111    |

| AF | BSTRA | AK                                                                  | iv     |

| A  | CKNO  | OWLEDGMENTS                                                         | v      |

| DE | DICA  | ATION                                                               | vi     |

| TA | BLE   | OF CONTENT                                                          | vii    |

| LI | ST OF | FTABLES                                                             | ix     |

| LI | ST OF | FFIGURES                                                            | x      |

| LI | ST OF | FABREVIATIONS                                                       | xiv    |

| LI | ST OF | F SYMBOLS                                                           | XV     |

| LI | ST OF | FPUBLICATIONS                                                       | xvi    |

| CI | IAPTI | ER                                                                  |        |

| 1. | INT   | RODUCTION                                                           | 1      |

|    | 1.1   | Introduction                                                        | - 1 ár |

|    | 1.2   | IEEE Standard 519                                                   | 3      |

|    | 1.3   | Problem Statement                                                   | 4      |

|    | 1.4   | Motivation of Research                                              | 5      |

|    | 1.5   | Objectives of Research                                              | 6      |

|    | 1.6   | Contributions of Research                                           | 6      |

|    | 1.7   | Scope of the Research                                               | 7      |

|    | 1.8   | Organization of the Dissertation                                    | 8      |

| 2. | LIT   | ERATURE REVIEW OF MULTILEVEL INVERTER                               | 9      |

|    | 2.1   | Introduction                                                        | 9      |

|    | 2.2   | Multilevel Inverter Topologies                                      | 14     |

|    |       | 2.2.1 Multilevel Diode Clamped/Neutral Point Inverter, NPCMLI       | 14     |

|    |       | 2.2.2 Multilevel Capacitor Clamped/Flying Capacitor Inverter, CCMLI | 20     |

|    |       | 2.2.3 Cascaded H- Bridge Multilevel Inverter, CHBMLI                | 24     |

|    | 2.3   | Combinational Topologies                                            | 28     |

|    |       | 2.3.1 Cascaded Diode-Clamped Multilevel Inverters                   | 28     |

|    |       | 2.3.2 Cascaded Multilevel H-bridge Inverters                        | 30     |

|    |       | 2.3.3 Cascaded Diode. Clamped / H-bridge Multilevel Inverter        | 31     |

|    | 2.4   | Control Techniques for Multilevel Inverters                         | 32     |

|    |       | 2.4.1 PWM for Two-level Inverters                                   | 33     |

|    |       | 2.4.2 Pulse Width Modulation (PWM) Techniques                       | 35     |

|    |       | 2.4.3 Sinusoidal Pulse-Width Modulation                             | 36     |

|    |       | 2.4.4 Space Vector PWM (SVPWM)                                      | 40     |

|    | 2.5   | Selective harmonic elimination for multilevel inverters             | 42     |

| 2  | DEC   | ICN MODEL MULTH EVEL INVEDTED FOR SIMULATION RASER                  | -      |

3. DESIGN MODEL MULTILEVEL INVERTER FOR SIMULATION BASED ON MATLAB/SIMULINK 46

vii

|    | 3.1 Intro | duction                                                                                                        | 4        |

|----|-----------|----------------------------------------------------------------------------------------------------------------|----------|

|    | 3.2 Mult  | ilevel Inverters with Pulse Width Modulation PWM Methods                                                       | 4        |

|    |           | soidal Pulse Width Modulation (SPWM)                                                                           | 4        |

|    |           | els of Diodes Clamped in Multilevel Inverter                                                                   | 5        |

|    |           | Steps in Modeling of Diodes Clamped                                                                            | 5        |

|    |           | Step 1 - Creating Signal Generator Block                                                                       | 5        |

|    | 3.5.2     | Step 2 -Multilevel Inverter block                                                                              | 6        |

|    | 3.5.3     | Step 3 - Completed model simulation block                                                                      | 7        |

|    |           | els of Cascaded H-Bridge in Multilevel Inverter                                                                | 7        |

|    | 3.7 The S | Steps in Modeling of Cascaded H-Bridge                                                                         | 7        |

|    | 3.7.1     | Step 1 - Creating Signal Generator Block                                                                       | 7        |

|    | 3.7.2     | Step 2 -Multilevel Inverter block                                                                              | 8        |

|    | 3.7.3     | Step 3 - Completed model simulation block                                                                      | 8        |

|    | 3.8 Harm  | onic Reduction by Increasing the Number of Voltage level in Mul-                                               | tilevel  |

|    | Inver     | ters                                                                                                           | 8        |

|    | 3.8.1     | 5-level multilevel inverters                                                                                   | 8        |

|    | 3.8.2     | 7-level multilevel inverters                                                                                   | 8        |

|    | 3.8.3     | 9-level multilevel inverters                                                                                   | 8        |

| 4. | SIMULATI  | ON RESULTS AND DISCUSSION ON THE MULTILEVEL                                                                    |          |

|    | INVERTER  | 성상을 가지 않는 것 같아요. 것 같아요. 이 것 같아요. 것 것 같아요. 것 같아요. 한 것 같아요. 것 같아요. 것 같아요. 전 바람이 나는 것 같아요. 것 같아요. 것 같아요. 것 같아요. 것 | 9        |

|    | 4.1       | Introduction                                                                                                   | 9        |

|    | 4.2       | Simulation Results                                                                                             | 9        |

|    | 4.3       | Diode Clamped in Multilevel Inverter Results                                                                   | 9        |

|    | 4.4       | Cascaded H-Bridge in Multilevel Inverter Results                                                               | 10       |

|    |           | TEFE 0. 1 1                                                                                                    | 11       |

|    | 4.5       | IEEE Standard                                                                                                  | 11       |

| 5. |           | ION AND FUTURE RESEARCH                                                                                        | 11       |

| 5. |           | ON AND FUTURE RESEARCH                                                                                         | 11       |

| 5. | CONCLUS   |                                                                                                                |          |

|    | CONCLUS   | ON AND FUTURE RESEARCH<br>Conclusion<br>Future of Research                                                     | 11<br>11 |

viii

# LIST OF TABLES

TABLE

| 1.1 | Harmonic voltage distortion limits                                | 4            |

|-----|-------------------------------------------------------------------|--------------|

| 2.1 | Switching states of one five-level phase leg.                     | 16           |

| 2.2 | The voltage and current paths in inverter switches                | 18           |

| 2.3 | Switching states for a five level Capacitor Clamped Inverter.     | 21           |

| 3.1 | Pole voltage and line Voltage of a Five Level Inverter            | 54           |

| 3.2 | Pole voltage and line Voltage of a Seven Level Inverter.          | 56           |

| 3.3 | Pole voltage and line Voltage of a Nine Level Inverter            | 59           |

| 3.4 | Parameters of Diodes Clamped in Multilevel Inverters (NPC).       | 66           |

| 3.5 | Pole voltage and line Voltage of a Five Level Inverter.           | 71           |

| 3.6 | Pole voltage and line Voltage of a Seven Level Inverter.          | 73           |

| 3.7 | Pole voltage and line Voltage of a Nine Level Inverter.           | 75           |

| 3.8 | Parameters of Cascaded H-Bridge in Multilevel Inverters (CHB).    | 80           |

| 3.9 | Minimizes Harmonic                                                | 92           |

| 4.1 | Comparison of diodes clamped and cascaded H-Bridge inverters with | th different |

|     | modulation index (mi=0.95, mi=0.8).                               | 113          |

| 4.2 | Harmonic voltage distortion limits                                | 114          |

|     |                                                                   |              |

íx

# LIST OF FIGURES

| FIGURE | TITLE                                                                       | PAGE     |

|--------|-----------------------------------------------------------------------------|----------|

| 2.1    | One phase leg of a two-level inverter and a two-level waveform without PWM  | И. 10    |

| 2.2    | PWM voltage output, reference wave in dashed blue.                          | 10       |

| 2.3    | A three-level waveform, a five-level waveform and a seven-level multilevel. | 11       |

| 2.4    | One phase leg of a three-level inverter.                                    | 12       |

| 2.5    | One phase-leg for a five-level NPC Inverter.                                | 15       |

| 2.6    | The voltage and current path in switches                                    | 17       |

| 2.8    | A Capacitor Clamped Multilevel Inverter with ve voltage levels.             | 20       |

| 2.9    | The current flows through the capacitors and switches out to the load.      | 22       |

| 2.10   | A five-level Cascaded Multilevel Inverter.                                  | 25       |

| 2.11   | Cascade 3/3 Multilevel Inverter.                                            | 29       |

| 2.12   | Cascaded Multilevel H-Bridge Inverter.                                      | 31       |

| 2.13   | Cascaded Diode-Clamped / H-bridge Multilevel inverter.                      | 32       |

| 2.14   | PWM reference (blue dashed) and triangular carrier (green solid) wave in up | per plot |

|        | and output voltage (green solid) eave in lower plot.                        | 34       |

| 2.15   | Classification of Multilevel Modulators methods.                            | 35       |

| 2.16   | Sinusoidal Pulse-Width Modulation.                                          | 37       |

| 2.17   | modified sinusoidal PWM technique.                                          | 38       |

| 2,18   | Sinusoidal Pulse-Width Modulation for Nine levels Inverter.                 | 40       |

| 2.19   | General Construction of the Multilevel Inverter.                            | 45       |

| 3.1.   | Block Diagram of the three Phase Multilevel Inverter.                       | 47       |

| 3.2    | Sinusoidal Pulse Width Modulation for three-phase inverter.                 | 51       |

| 3.3    | Diode Clamped of Multilevel Inverter Three-phase Five-level.                | 52       |

| 3.4    | Five-level Output Voltage of Diode Clamped Multilevel Inverter.             | 52       |

| 3.5    | Diode Clamped of Multilevel Inverter Three-phase Seven-level.               | 55       |

| 3.6    | Seven-level Output Voltage of Diode Clamped Multilevel Inverter.            | 56       |

| 3.7   | Diode Clamped of Multilevel Inverter Three-phase Nine-level.                   | 57    |

|-------|--------------------------------------------------------------------------------|-------|

| 3.8   | Nine-level Output Voltage of Diode Clamped Multilevel Inverter.                | 58    |

| 3.9.  | Modulating signal generation of Diode Clamped Multilevel Inverter.             | 60    |

| 3.10. | Three-Phase Modulating Signal Generation Diode Clamped Inverter.               | 60    |

| 3.11. | Simulink Multilevel Inverter diagram Five Level of control signal generation D | liode |

|       | Clamped.                                                                       | 62    |

| 3.12. | Simulink Multilevel Inverter diagram Seven Level of control signal generation  | ation |

|       | Diode Clamped.                                                                 | 63    |

| 3.13. | Simulink Multilevel Inverter diagram Nine Level of control signal generation D | liode |

|       | Clamped.                                                                       | 64    |

| 3,14  | Gate Turn Off (GTO) Thyristor.                                                 | 65    |

| 3.15  | Switch Controlled Signal GTO Thyristor.                                        | 65    |

| 3.16  | Switching GTO Thyristor for five Levels Diode Clamped Multilevel Inverter.     | 67    |

| 3.17  | Switching GTO Thyristor for Seven Levels Diode Clamped Multilevel Inverter.    | 68    |

| 3.18  | Switching GTO Thyristor for Nine Levels Diode Clamped Multilevel Inverter.     | 68    |

| 3.19  | Block Nine-Levels of Diode Clamped Multilevel Inverter                         | 69    |

| 3.20  | Simulation of Nine-level Diode Clamped Multilevel Inverter.                    | 70    |

| 3.21  | Cascaded H-Bright of Multilevel Inverter Three-Phase Five-level.               | 72    |

| 3.22  | Output voltage waveforms of a five-level Cascaded H-Bridge                     | 72    |

| 3.23  | Cascaded H-Bridge of Multilevel Inverter Three-phase Seven-level,              | 74    |

| 3.24  | Output voltage waveforms of a Seven-level Cascaded H-Bridge.                   | 74    |

| 3.25  | Cascaded H-Bridge of Multilevel Inverter Three-phase Nine-level                | 76    |

| 3.26  | Nine-level Cascaded H-Bridge Inverter Waveforms.                               | 76    |

| 3.27  | Modulating signal generation of Cascaded H-Bridge Multilevel Inverter.         | 77    |

| 3.28  | Simulink Five Level of control signal Cascaded H-Bridge Multilevel Inverter.   | 78    |

| 3.29  | Simulink Seven Level of control                                                | 79    |

| 3.30  | Simulink Nine Level of control signal Cascaded H-Bridge Inverter.              | 79    |

| 3.31  | Switching GTO Thruster for Nine Levels Cascaded H-Bridge Multilevel Inverter.  | 81    |

| 3.32  | Block Nine-Levels of Cascaded H-Bridge Multilevel Inverter.                    | 82    |

| 3.33  | Simulation of Nine-level Cascaded H-Bridge Multilevel Inverter.                | 83    |

| 3.33  | Simulation of Nine-level Cascaded H-Bridge Multilevel Inverter.                |       |

| 4.1. | Phase Voltage MI=0.95.    | 94  |

|------|---------------------------|-----|

| 4.2  | Phase Voltage MI= 0.8     | 95  |

| 4.3  | Line Voltage MI=0.95.     | 95  |

| 4.4  | Line Voltage MI=0.8.      | 96  |

| 4.5  | Harmonic Voltage MI=0.95. | 96  |

| 4.6  | Harmonic Voltage MI=0.8.  | 97  |

| 4.7  | Phase Voltage MI=0.95.    | 98  |

| 4.8  | Phase Voltage MI=0.8      | 98  |

| 4.9  | Line Voltage MI=0.95.     | 99  |

| 4.10 | Line Voltage MI=0.8.      | 99  |

| 4.11 | Harmonic Voltage MI=0.95. | 100 |

| 4.12 | Harmonic Voltage MI=0.8.  | 100 |

| 4.13 | Phase Voltage MI=0.95.    | 101 |

| 4.14 | Phase Voltage MI=0.8.     | 101 |

| 4.15 | Line Voltage MI=0.95.     | 102 |

| 4.16 | Line Voltage MI=0.8.      | 102 |

| 4.17 | Harmonic Voltage MI=0.95. | 103 |

| 4.18 | Harmonic Voltage M=0.8.   | 103 |

| 4.19 | Phase Voltage MI=0.95.    | 104 |

| 4.20 | Phase Voltage MI=0.8.     | 104 |

| 4.21 | Line Voltage MI=0.95.     | 105 |

| 4.22 | Line Voltage MI=0.8.      | 105 |

| 4.23 | Harmonic Voltage MI=1.    | 106 |

| 4.24 | Harmonic Voltage MI=0.8.  | 106 |

| 4.25 | Phase Voltage MI=0.95.    | 107 |

| 4.26 | Phase Voltage MI=0.8.     | 107 |

| 4.27 | Line Voltage MI=0.95.     | 108 |

| 4.28 | Line Voltage MI=0.8.      | 108 |

| 4.29 | Harmonic Voltage MI=0.95. | 109 |

| 4.30 | Harmonic Voltage MI=0.8.  | 109 |

|      | vii                       |     |

xii

| 4.31 | Phase Voltage MI=0.95.    | 110 |

|------|---------------------------|-----|

| 4.32 | Phase Voltage MI=0.8.     | 110 |

| 4.33 | Line Voltage MI=0.95.     | 111 |

| 4.34 | Line Voltage MI=0.8.      | 111 |

| 4.35 | Harmonic Voltage MI=0.95. | 112 |

| 4.36 | Harmonic Voltage MI=0.8.  | 112 |

xiii

# LIST OF ABREVIATIONS

| AC       | ÷    | Alternating Current                             |

|----------|------|-------------------------------------------------|

| DC       | 14   | Direct Current                                  |

| THD      | ÷    | Total Harmonic Distortion                       |

| THDv     | -    | Voltage Total Harmonic Distortion               |

| IGBT     | -    | Insulated Gate Bipolar Transistor               |

| GTO      | -    | Gate turn-off                                   |

| PDM      | 1200 | Pulse-Duration Modulation                       |

| PWM      |      | Pulse Width Modulation                          |

| SPWM     |      | Sinusoidal Pulse Width Modulation               |

| MI       | -    | Modulation Index                                |

| Vdc      |      | Voltage Direct Current                          |

| IEEE STD |      | Institute of Electrical and Electronic Engineer |

| MLI      |      | Multilevel Inverter                             |

| NPCMLI   |      | Neutral-Point Clamped Multilevel Inverter       |

| CCMLI    | 4    | Flying Capacitor Multilevel Inverter            |

| CHBMLI   | -    | Cascaded H- Bridge Multilevel Inverter          |

| CC       | ÷    | Clamped Capacitors                              |

| VCHB     |      | Voltage Cascaded H- Bridge                      |

| PD       |      | Phase Disposition                               |

| POD      | τ.   | Phase Opposition Disposition                    |

| RMS      | -    | Root Mean Square                                |

|          |      |                                                 |

xiv

# LIST OF SYMBOLS

| b                |    | Bias                             |

|------------------|----|----------------------------------|

| f                | ÷  | Frequency                        |

| F                | -  | Force                            |

| $\mathbf{F}_{f}$ | -  | Friction force                   |

| Frms             | 8  | Root mean square of force        |

| Finitial         | ÷  | Initial force                    |

| Ν                | -  | Normal fares                     |

| Ra               | -  | Arithmetic average roughness     |

| Rt               | A  | Roughness total                  |

| Rz               | -  | Ten-point mean roughness         |

| Т                | -  | Periods                          |

| t                | 4  | Time                             |

| w                | G  | Weight                           |

| x                | 1  | Horizontal Cartesian coordinates |

| у                | 3  | Vertical Cartesian coordinates   |

| μ.               | 1  | Coefficient of kinetic friction  |

| $\mu_s$          | 2  | Coefficient of static friction   |

| $\mu_{\theta}$   | ÷. | Population mean                  |

| x                | 8  | Mean of data                     |

| Σ                | *  | Summation                        |

| π                | S  | Phi (3,14)                       |

| ω                | ÷  | Rotational speed                 |

| σ                | 9  | Standard deviation               |

| θ                | 6  | Threshold                        |

| φ                | 5  | Activation function              |

| a                |    | Significance level               |

XV

### Published

- Rosli Omar, Mohammed Rasheed, Ahmed Al-janad, Marizan Sulaiman "Fundamental Studies of a Three Phase Cascaded H-Bridge and Diode Clamped Multilevel Inverters Using Matlab/Simulink" Vol. 6, N.5 Sep 2013 (I.RE.A.CO.) Available at http://www.praiseworthyprize.com/IREACO-latest/IREACO vol 6 n 5.html

- Rosli Omar, Mohammed Rasheed, Ahmed Al-janad, Marizan Sulaiman "Harmonic Reduction for Diode Clamped and Cascaded H-Bright Five to Nine Level of Multilevel Inverters Application, Australian Journal of Basic and Applied Sciences (AJBAS), March 2014. Available at: <u>http://ajbasweb.com/old/ajbas/2014/March/211-227.pdf</u>

- R. Omar, A. Aljanad, M. Rasheed, M. H. Mustapha, "Analyzing Performance of Super-Capacitor and Battery in Low Voltage Electric Distribution System", Journal of Theoretical and Applied Information Technology, Vol. 61. No., 10 March 2014, Available at: http://www.jatit.org/volumes/Vol61No1/12Vol61No1.pdf

- M. Rasheed, R. Omar, A. Aljanad, M. Sulaiman, A. Ahmed, 2013. "Performance Studies of Three-Phase Cascaded H-Bridge and Diode-Clamped Multilevel inverters" 2013 IEEE Conference on Clean Energy and Technology (CEAT) Available At: http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=6775641

xvi

- Rosli Omar, Mohammed Rasheed, Ahmed Al-Janad, Marizan Sulaiman, Zulkifilie. Ibrahim, "Harmonic Reduction Comparison in Multilevel Inverters for Industrial Application" Journal of Theoretical and Applied Information Technology" Vol. 63. No., 3 May 2014. Available At: http://www.jatit.org/volumes.php

- Rosli Omar, Mohammed Rasheed, Marizan Sulaiman, Ahmed Al-Janad, "A Study of a Three Phase Diode Clamped Multilevel Inverter Performance for Harmonics Reduction" Bris Journal of Advances in Science & Technology" May 2014 issue. Not Publish Yet

- A. Aljanad, R. Omar, M. Rasheed, Z. Ibrahim," Performance Analyzing of Super-Capacitor and Battery as Storage Energy in Voltage Source Inverter", International Review on Modeling and Simulations (I.RE.A.), vol. 1 n° 6, November 2013, Available at:http://www.praiseworthyprize.it/public/eIREA/feedback.asp?user=irea016002&review =irea\_vol.1\_n.6

- Al-janad, A., Omar, R., M Rasheed., Ahmed, Azhar, "Comparative study of super capacitor and battery as storage energy in three phase system" 2013 IEEE Conference on Clean Energy and Technology (CEAT) Available At: http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=6775611

xvii

### CHAPTER 1

#### INTRODUCTION

#### 1.1 Introduction

Nowadays, multilevel inverters have become more attractive for their initial usage in high-voltage and high-power applications. Multilevel converters (or inverters) have been used for AC to DC, AC to DC to AC, DC to AC, and DC to DC power conversions in high power applications such as utility and large motor drive applications (Peng, 2001). Multilevel inverters provide more than two voltage levels. The generalized multilevel inverter topology can balance each voltage level by itself regardless of the inverter control and load characteristics. The concept of multilevel converters has been introduced since 1975 (Karuppanan, 2011). The usage of these applications has become more diverse and affects a wide field of electrical engineering from a few watts to several hundred megawatts. Converting static structures that comprise mainly applications of power electronics is becoming increasingly powerful, and the technology has had to adapt to the growth of the power to convert. This growth has been possible to the development of technologies of semiconductor components. Changing templates voltage and current, as well as improved performance of these components, has to use more power electronics performance for applications of greater power (Colak, 2010). However, the performance of current components do not allow for an optimum conversion of electrical energy. Indeed, the increase in tension is often used to improve yields. However, the use of components with templates in high voltage does not improve the overall efficiency of the plant, or even worse, because these components

are generally underperform components templates voltage lower, and thus, produce more losses (Axelrod, 2005). Hence, to solve this problem, more efficient components are used and new structures have been developed. These structures are known as multilevel inverters, and they have more than two output levels of voltages. They were created at the first time to be able both to be several switches in series, and ensure properly withstand voltage across them later, as these inverters showed an interesting property on the output waveforms. The rotary electric actuators play a very important role in the industry and particularly in electric traction. The performance required for these actuators is high, both in terms of the dynamics of the speed and the precision of torque delivered (Xu et al, 2004). The DC machine has been used to make the most of these actuators given the simplicity the order. However, the current machine has several drawbacks associated with its mechanical commutators. In contrast, AC machines (synchronous and asynchronous) possess many advantages. The absence of collector allows them to have a smaller footprint, increased reliability, and high operating speed. Indeed, the permanent magnet synchronous machine is distinguished by its excellent performance and its large mass couple is allowed to prevail in applications that require very high static and dynamic performance, particularly in areas of applications such as flexible manufacturing systems, robotics, aeronautics, and space (Babaei, 2013). The emergence and development of new components for controllable powers opening and closing as the GTO (gate turn-off Thyristor) and IGBT (insulated gate bipolar transistors) allow the design of new converters to be reliable, fast, and powerful. Thus, all drives (static machine converter current AC) costs are reduced considerably. Progress in the field of the microcomputer (fast and powerful microcontrollers) allows the synchronized control algorithms of these sets to be more efficient converter machine and robust (Chen, 2004). The Pulse Width Modulation (PWM) is a technique to control static converters for interfacing between a load (electrical machine) and

supply means (three-phase inverter). It is a technique used for energy conversion, having its base in the field of telecommunications (signal processing). It can possibly name as Pulse Width Modulation (PWM) or Pulse-Duration Modulation (PDM). Far from being an accessory element in the chain of variable speed (inverter power associated with an electric machine), the PWM stage plays an important role with impact on the performance of all system performance driving, loss in the inverter or the machine, the acoustic noise, electromagnetic noise, even the destruction of the system, e.g. due to over voltages which occur during the use of long cables (Du et al, 2007).

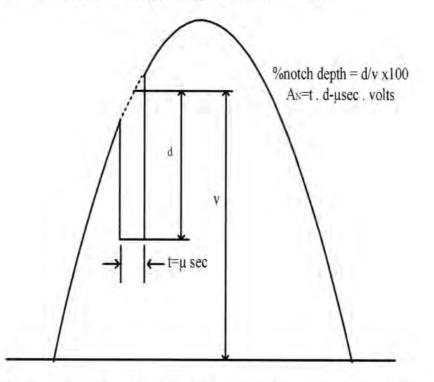

#### 1.2 IEEE Standard 519

The IEEE Standard 519 was introduced in 1981 and most-recently has been revised in 1992. It is intended to provide direction on dealing with harmonics introduced by nonlinear loads. The standard recognizes the responsibility of an electricity user not to distort the voltage of the utility by drawing heavy nonlinear or distorted currents. It also recognizes the responsibility of the utility to provide the users with a near-sine-wave voltage. Table 1.1 shows the distortion limits for both current and voltage are defined in order to minimize interference between electrical equipment, in Figure 1.1 definition of notch depth and notch area. It is presented as a guideline for power system design when nonlinear loads are presented. IEEE STD 519 establishes harmonic limits on voltage as 5% for total harmonic distortion and 3% of the fundamental voltage for any single harmonic (Almarghani, 2009).

|               | Special Applications* | General system | Dedicated System |

|---------------|-----------------------|----------------|------------------|

| Notch Depth   | 10%                   | 20%            | 50%              |

| THD (voltage) | 3%                    | 5%             | 10%              |

| Notch Area    | 16,400                | 22,800         | 36,500           |

Table 1.1: Harmonic voltage distortion limits

It is considered from Table 1.1 that  $A_N$  value for other than 480-volt systems should be

multiplied by V/480, and its unit is represented in microsecond\*volts.

Figure 1.1: Definition of Notch Depth and Notch Area (Handbook, 2000)

### 1.3 Problem Statement

One of the major problems with electric power quality is the harmonic contents. There are several methods of indicating the quantity of harmonic contents. The main focus is measuring the total harmonic distortion (THD). In electrical systems, the inverters are used to

convert DC voltage to AC voltage, but it has been noticed that the voltage from the inverter does not produce smooth waveform, but rather a discrete waveform. As a result, it is more likely that the output waveform consists of harmonics, which are not usually desirable since they deteriorate the performance of the load. There are also other topologies for inverters such as multilevel inverters. The main idea of multilevel inverters is to have a better sinusoidal voltage and current in the output by using switches in series. Since many switches are put in series, the switching angles are important in the multilevel inverters because all of the switches should be switched in such a way that the output voltage and current have low harmonic distortion.

There are 3 types of multilevel inverters which are diode clamped multilevel inverters, flying capacitor multilevel inverters, and cascaded H-bridge multilevel inverter. In this dissertation, two types of multilevel inverters; diode clamped multilevel inverters and cascaded H-bridge multilevel inverter, were constructed and ensuring the approach of less switches and acquired low harmonic distortion.

#### 1.4 Motivation of Research

With the development of power electronics and the proliferation of non-linear loads in the applications of industrial power, the issue of harmonic contents and their effects on power quality are important topics to be studied. Proper strategy should be implemented to minimize harmonic problems to avoid the system to become worse. In recent years, there is an increase in interest of multilevel power conversation. Recent researches have introduced novel converter topologies and unique modulation strategies, and because of its diverse applications, the multilevel inverter has become the most-used and analysed topology in the power