# **Faculty Of Electronics and Computer Engineering**

## FAULT ANALYSIS AND TEST FOR BRIDGE DEFECT IN RESISTIVE RANDOM ACCESS MEMORY

Norsuhaidah binti Arshad

Master of Science in Electronic Engineering

2016

C Universiti Teknikal Malaysia Melaka

# FAULT ANALYSIS AND TEST FOR BRIDGE DEFECT IN RESISTIVE RANDOM ACCESS MEMORY

### NORSUHAIDAH BINTI ARSHAD

A thesis submitted in fulfilment of the requirements for the degree of Master of Science in Electronic Engineering

Faculty of Electronic and Computer Engineering

### UNIVERSITI TEKNIKAL MALAYSIA MELAKA

2016

C Universiti Teknikal Malaysia Melaka

### DECLARATION

I declare that this entitled "Fault Analysis and Test for Bridge Defect In Resistive Random Access Memory" is the result of my own research except as cited in the references. The thesis has not been accepted for any degree and is not concurrently submitted in candidature of any other degree.

| Signature | : |

|-----------|---|

| Name      | : |

| Date      | : |

### APPROVAL

I hereby declare that I have read this thesis and my opinion this thesis is sufficient in term of scope and quality for the award of Master of Science in Electronic Engineering.

| Signature       | · |

|-----------------|---|

| Supervisor Name | · |

| Date            | · |

### DEDICATION

To my charming husband

To my beloved mother, father and sister

To my supportive late supervisor

### ABSTRACT

Resistive Random-Access Memory (ReRAM) is one of the potential candidates of emerging semiconductor memory to replace the conventional memory technologies. Besides, ReRAM offers many attractive advantages, such as non-volatile, scalable, low power consumption, and fast data access. Due to the infancy stage of this emerging memory, ReRAM is prone to have bridge defects that could lead to test escape and reliability issues. Moreover, with the lack of electrical model for ReRAM, this research presents an electrical ReRAM model that was designed with SILVACO Electronic Design Automation (EDA) software. All ReRAM elements designed used 22nm Complementary Metal Oxide Semiconductor (CMOS) transistors and a novel non-CMOS device, known as memristor, as the memory cell array. The optimal memristor model that had been proposed by D. Biolek was chosen among three published memristor SPICE models. The selection was made based on the performance analysis. Furthermore, simulation of 2x2 cell ReRAM was executed in order to prove the functionality of the design. The designed ReRAM model functioned as desired based on the simulation results. In addition, the defective behaviors of the faulty ReRAM that were impacted by the three types of bridge defects, (bridge between wordlines; BW, bridge between bitlines; BB and bridge between bitlines and wordlines; BBW) had been studied in this work. The faulty ReRAM model was established by injecting the defects into the designed electrical ReRAM model. As this ReRAM employed a non-CMOS device as its memory cells, the defect that occurred might behave differently than that happens in conventional memories. This could cause the faulty ReRAM to escape from the available memory test. The simulation of the faulty ReRAM model showed that the bridge defects had been due to the Undefined State Faults (USFs) during reading operation. Besides, any faulty in ReRAM caused by USF makes setting the cell to the desired logical value a challenging task, and this fault is difficult to be detected. Hence, a new Design-for-Testability (DfT) technique was proposed to detect these USFs. This technique, known as Adaptive Sensing Read Voltage (ASRV), had been developed based on the mechanism of memristor, as well as the function of sense amplifier. Apart from that, a slight circuit modification was done to implement the DfT circuitry. Based on the simulation results during the DfT implementation, the proposed DfT technique successfully detects the USFs that occurred when  $0\Omega \le R_{BW} \le 50\Omega$  for BW injection,  $36\Omega \le R_{BB} \le 372\Omega$  for BB injection and  $140\Omega \le R_{BBW} \le 210\Omega$  for BBW injection. However, this DfT technique might not suitable for BBW injection as it might kill the healthy cell.

i

### ABSTRAK

Memori rintangan Random Access (ReRAM) adalah salah satu calon potensi memori semikonduktor baru yang muncul untuk menggantikan teknologi memori konvensional. ReRAM menawarkan banyak kelebihan menarik seperti tidak meruap, boleh skala, penggunaan tenaga yang rendah, dan akses data yang cepat. Oleh kerana memori baru ini masih di peringkat awal, ReRAM ini mempunyai kecacatan jambatan yang boleh memyebabkannya terlepas daripada ujian dan masalah kebolehpercayaan. Disebabkan oleh kekurangan model elektrik untuk ReRAM, kajian ini membentangkan model ReRAM elektrik yang direka menggunakan perisian SILVACO Elektronik Design Automation (EDA). Semua unsur-unsur ReRAM direka menggunakan transistor 22nm Oksida Logam Pelengkap Semiconductor transistor dan peranti baru yang bukan CMOS dikenali sebagai memristor pelbagai sel memori. Optimum model memristor yang dicadangkan oleh D. Biolek dipilih daripada tiga memristor model SPICE yang telah diterbitkan. Pemilihan dibuat berdasarkan analisis prestasi. Simulasi sel 2x2 ReRAM dilaksanakan untuk membuktikan fungsi rekabentuk. Model ReRAM yang direka berfungsi seperti yang dikehendaki berdasarkan keputusan simulasi. Tingkah laku yang cacat bagi ReRAM cacat yang terkesan oleh tiga jenis kecacatan jambatan (jambatan antara wordlines; BW, jambatan antara bitline; BB, dan jambatan antara bitlines dan wordlines; BBW) dikaji dalam kerja-kerja ini. Model ReRAM cacat ditubuhkan dengan menyuntik kecacatan dalam model ReRAM elektrik yang direka. Memandangkan ReRAM ini menggunakan alat bukan CMOS sebagai sel-sel ingatan, kecacatan yang berlaku mungkin berkelakuan berbeza daripada yang berlaku dalam memori konvensional. Ini boleh menyebabkan terlepasnya ReRAM cacat dari ujian memori yang tersedia. Simulasi untuk model ReRAM yang cacat menunjukkan bahawa kecacatan jambatan menyebabkan timbulnya Kerosakan Keadaan Tidak Ditakrif (USFs) semasa operasi dibaca. USFs akan menyebabkan sel ReRAM yang cacat sukar untuk ditetapkan kepada nilai logik yang dikehendaki dan kerosakan ini adalah sukar untuk dikesan. Oleh itu, rekabentuk untuk kebolehujian teknik (DfT) yang baru dicadangkan untuk mengesan USFs ini. Teknik ini dinamakan sebagai Penyesuaian Penderiaan Bacaan Voltan (ASRV) yang dibangunkan berdasarkan mekanisme memristor dan fungsi pengesan penguat. Sedikit pengubahsuaian litar dilakukan untuk melaksanakan litar DfT. Berdasarkan keputusan simulasi semasa pelaksanaan DfT, teknik DfT yang dicadangkan berjaya mengesan USFs apabila  $0\Omega \leq R_{BW} \leq 50\Omega$  untuk suntikan BW,  $36\Omega \leq R_{BB} \leq 372\Omega$  untuk suntikan BB dan  $140\Omega \leq R_{BBW} \leq 210\Omega$  untuk suntikan BBW. Walau bagaimanapun, teknik DfT ini mungkin tidak sesuai untuk suntikan BBW kerana ia mungkin membunuh sel yang sihat.

### ACKNOWLEDGEMENTS

In the name of Allah, the Most Gracious and the Most Merciful, all praises and thanks to Allah as I have finally completed this thesis successfully. First of all, I would like to express my appreciation to my late supervisor, Allayarham Dr Nor Zaidi bin Haron, for his kindness, encouragement, and guidance throughout the journey of this research. His willingness to educate me the art of well-organized technical writing, as well as showering wisdom in giving ideas to solve problems earned my admiration. It was indeed a great pleasure to have had the opportunity to conduct this research under his supervision. May his soul rest in peace. On the other hand, I would like to acknowledge my new supervisor, Dr Fauziyah binti Salehuddin, who had been so supportive towards me to complete my thesis. Thank you for your time to read and to review my thesis. On top of that, my appreciation also goes to my new co-supervisor, En Sani Irwan bin Salim; and project's mentor, PM Norhayati binti Soin from Universiti Malaya who also encouraged and spent some time to review my thesis.

Next, I would like to acknowledge the Faculty of Electronics and Computer Engineering for providing me the facilities for this research. Also, thanks to KPT for supporting this project financially under the Fundamental Research Grant Scheme (FRGS). Last but not least, my deepest appreciation goes to my charming husband, Muhammad Fadhle Ikram; parents, Arshad and Nor Rizan; and my beloved siblings, for their understanding, prayers, love, and support that expressively led to my achievement. Not to forget my colleagues in the laboratory for their kind help and opinion throughout the preparation of this thesis. Lastly, many thanks to all who have helped directly or indirectly upon the accomplishment of this research.

### **TABLE OF CONTENT**

26

| DEC  | LAR         | ATION  |                                          |             |

|------|-------------|--------|------------------------------------------|-------------|

| APPI | ROV         | 4L     |                                          |             |

| DED  | ICAT        | TION   |                                          |             |

| ABS  | <b>FRAC</b> | CT     |                                          | i           |

| ABS  | ſRAŀ        | K      |                                          | ii          |

| ACK  | NOW         | /LEDG  | MENT                                     | iii         |

| TAB  | LE O        | F CON  | TENT                                     | iv          |

| LIST | OF 1        | ГАВLE  | S                                        | vii         |

| LIST | OF I        | FIGUR  | ES                                       | viii        |

| LIST | OF A        | ABBRE  | CVIATIONS                                | xi          |

| LIST | OF I        | PUBLIC | CATIONS                                  | xii         |

| СНА  | ртеі        | R      |                                          |             |

| 1.   |             |        | CTION                                    | 1           |

|      | 1.1         |        | rch Background                           | 1           |

|      |             |        | em Statement                             | 2           |

|      |             | Object |                                          | 4           |

|      |             |        | of Research                              |             |

|      | 1.5         | -      | ibutions                                 | 4<br>5<br>5 |

|      |             | 1.5.1  | ReRAM Electrical Model                   | 5           |

|      |             | 1.5.2  | Faulty Models for Bridge Defect in ReRAM | 6           |

|      |             |        | Dft Technique for Bridge Defect in ReRAM | 6           |

|      | 1.6         |        | s Organizations                          | 6           |

| 2.   | LIT         | ERATI  | URE REVIEW                               | 8           |

|      | 2.1         |        |                                          | 8           |

|      | 2.2         |        | bry Technologies                         | 8           |

|      |             |        | Memory Concept                           | 9           |

|      |             |        | Memory Technology Classification         | 10          |

|      | 2.3         |        | entional Memory Technology               | 11          |

|      |             |        | SRAM                                     | 12          |

|      |             | 2.3.2  | DRAM                                     | 13          |

|      |             |        | Masked ROM                               | 13          |

|      |             |        | OTP PROM                                 | 14          |

|      |             | 2.3.5  | EPROM                                    | 14          |

|      |             | 2.3.6  | EEPROM                                   | 14          |

|      |             | 2.3.7  | Flash                                    | 15          |

|      | 2.4         | Emerg  | ging Memory Technologies                 | 15          |

|      |             |        | FRAM                                     | 16          |

|      |             | 2.4.2  | MRAM                                     | 17          |

|      |             |        | STTRAM                                   | 18          |

|      |             |        | PCRAM                                    | 19          |

|      |             |        | ReRAM                                    | 21          |

|      |             |        | ORAM                                     | 22          |

|      |             | 2.4.7  | Summary of Emerging Memory Technologies  | 23          |

2.5 Potentials and Challenges of ReRAM

|     | 2.5.1   | Potentials   | 8             |                                    | 26 |

|-----|---------|--------------|---------------|------------------------------------|----|

|     | 2.5.2   | Challenge    | es            |                                    | 29 |

| 2.6 | Backg   | round of R   |               |                                    | 30 |

|     | -       | Memory       |               |                                    | 31 |

|     |         |              | al ReRAM N    | Model                              | 33 |

|     |         |              | ReRAM M       |                                    | 34 |

|     |         | 2.6.3.1      |               |                                    | 34 |

|     |         | 2.6.3.2      | 2             | Memristor Model                    | 38 |

|     |         |              | 2.6.3.2.1     | Memristor Model Proposed by        | 38 |

|     |         |              | 2.0.0.2.1     | Joglekar <i>et al.</i>             | 20 |

|     |         |              | 2.6.3.2.2     | Memristor Model Proposed by        | 38 |

|     |         |              |               | Prodromakis <i>et al</i> .         |    |

|     |         |              | 2.6.3.2.3     | Memristor Model Proposed by Biolek | 39 |

|     |         |              | 2.0.0.2.2     | et al.                             | 57 |

|     |         | 2.6.3.3      | Peripheral    |                                    | 40 |

| 2.7 | Classif | fication of  | -             |                                    | 40 |

| ,   | 2.7.1   |              | n Memory C    | Cell Array                         | 42 |

|     | 2.,.1   | 2.7.1.1      | -             | ects in ReRAM Memory Cells         | 42 |

|     |         | 2.7.1.2      | 1             | efects in ReRAM Memory Cells       | 43 |

| 2.8 | Testin  | g Concepts   | •             |                                    | 44 |

| 2.0 |         | Key Tern     |               |                                    | 44 |

|     | 2.0.1   | -            | Defect        |                                    | 45 |

|     |         | 2.8.1.2      |               |                                    | 45 |

|     |         | 2.8.1.3      |               |                                    | 46 |

|     |         |              | Failure       |                                    | 46 |

|     |         | 2.8.1.5      | Quality       |                                    | 47 |

|     |         | 2.8.1.6      | Reliability   |                                    | 47 |

|     |         | 2.8.1.7      | Testing       |                                    | 47 |

|     | 2.8.2   |              | Manufacturi   | ng Flow                            | 48 |

|     | 2.8.3   | Memory       |               |                                    | 49 |

|     |         | 2.8.3.1      | -             | Test                               | 50 |

|     |         |              | March Test    |                                    | 50 |

|     |         |              | Structural 7  |                                    | 51 |

|     |         |              | Defect-orie   |                                    | 51 |

|     |         | 2.8.3.5      | Parametric    |                                    | 51 |

|     |         | 2.8.3.6      | Dynamic T     |                                    | 52 |

|     |         | 2.8.3.7      | Burn-in Te    |                                    | 52 |

|     | 2.8.4   |              | or-Testabilit |                                    | 52 |

|     |         | 2.8.4.1      |               | e Time (SWT) based DfT             | 52 |

|     |         | 2.8.4.2      |               | Voltage (LWV) based DfT            | 53 |

| 2.9 | Summ    |              |               |                                    | 54 |

| ME  | ГНОДО   | DLOGY        |               |                                    | 55 |

| 3.1 | Introdu | uction       |               |                                    | 55 |

| 3.2 | Flowe   | hart of Pro  | ject          |                                    | 55 |

| 3.3 | Optim   | ization of l | Memristor S   | PICE Model                         | 59 |

| 3.4 | Develo  | opment of ]  | ReRAM Ele     | ectrical Model                     | 64 |

| 3.5 | Develo  | opment of ]  | Faulty ReRA   | AM Electrical Model                | 71 |

| 3.6 | Develo  | opment of ]  | DfT Technie   | que                                | 77 |

| 3.7 | Summ    | ary          |               |                                    | 82 |

|     |         |              |               | V                                  |    |

3.

| 4.  | RES   | SULTS .        | AND DISCUSSION                                  | 83  |  |  |

|-----|-------|----------------|-------------------------------------------------|-----|--|--|

|     | 4.1   | 1 Introduction |                                                 |     |  |  |

|     | 4.2   | Result         | Results of Memristor SPICE Model Optimization   |     |  |  |

|     |       | 4.2.1          | Joglekar's Memristor Model                      | 85  |  |  |

|     |       | 4.2.2          | Prodromakis's Memristor Model                   | 87  |  |  |

|     |       | 4.2.3          | Biolek's Memristor Model                        | 87  |  |  |

|     |       | 4.2.4          | Summary of Memristor Model                      | 89  |  |  |

|     | 4.3   | Result         | ts of ReRAM Simulation Model Development        | 89  |  |  |

|     |       |                | Memory Array                                    | 90  |  |  |

|     |       |                | Row/column Decoder                              | 91  |  |  |

|     |       | 4.3.3          | Write/read Circuit                              | 92  |  |  |

|     |       | 4.3.4          | Sense Amplifier                                 | 93  |  |  |

|     |       |                | Defect-free Simulation                          | 95  |  |  |

|     | 4.4   |                | ts of Simulation in Fault Modeling              | 99  |  |  |

|     |       |                | BW Injection                                    | 99  |  |  |

|     |       |                | BB Injection                                    | 102 |  |  |

|     |       |                | BBW Injection                                   | 105 |  |  |

|     |       |                | Simulation Analysis for Faulty ReRAM Model      | 108 |  |  |

|     | 4.5   |                | ts of DfT Implementation                        | 110 |  |  |

|     |       |                | DfT Implementation for BW Injection             | 110 |  |  |

|     |       | 4.5.2          | DfT Implementation for BB Injection             | 113 |  |  |

|     |       |                | DfT Implementation for BBW Injection            | 116 |  |  |

|     |       | 4.5.4          | 5 1                                             | 120 |  |  |

|     | 4.6   | Summ           | lary                                            | 121 |  |  |

| 5.  | CO    | NCLUS          | ION AND FUTURE WORKS                            | 122 |  |  |

|     | 5.1   | Conclu         | usion                                           | 122 |  |  |

|     | 5.2   | Future         | Works                                           | 123 |  |  |

| REI | FERE  | NCES           |                                                 | 125 |  |  |

| APF | PENDI | XA             | - SYMBOL FOR MEMRISTOR MODEL                    | 133 |  |  |

| APF | PENDI | XB             | - 22NM CMOS TECHNOLOGY                          | 136 |  |  |

| APF | PENDI | XC             | - SIMULATION RESULTS DURING BRIDGE<br>INJECTION | 141 |  |  |

| APF | PENDI | X D            | - SIMULATION RESULTS DURING DFT                 | 149 |  |  |

|     |       |                | IMPLEMENTATION                                  |     |  |  |

### LIST OF TABLES

TITLE

PAGE

TABLE

| 2.1 | Summary of emerging memory technologies                             | 25  |

|-----|---------------------------------------------------------------------|-----|

| 2.2 | Features of conventional and emerging memory technologies           | 27  |

| 2.3 | Classification of defects                                           | 41  |

| 2.4 | Summary of DfT technique in ReRAM                                   | 54  |

| 3.1 | Observation of simulation results for resistive $(R_{bidge})$ value | 74  |

| 3.2 | Test algorithm                                                      | 76  |

| 3.3 | Parameter for DfT circuitry                                         | 81  |

| 4.1 | Summary for performance analysis among three memristor model        | 89  |

| 4.2 | Observed faults for BW injection                                    | 101 |

| 4.3 | Observed faults for BB injection                                    | 104 |

| 4.4 | Observed faults for BBW injection                                   | 107 |

| 4.5 | Observed fault models for bridge defects                            | 109 |

| 4.6 | Results of $R_{BW}$ before and after implementation of DfT          | 112 |

| 4.7 | Results of $R_{BB}$ before and after implementation of DfT          | 115 |

| 4.8 | Results of $R_{BBW}$ before and after implementation of DfT         | 117 |

| 4.9 | Comparison between ASRV technique and LWV technique                 | 120 |

C Universiti Teknikal Malaysia Melaka

### LIST OF FIGURES

| FIGU | TRE TITLE                                                  | PAGE |

|------|------------------------------------------------------------|------|

| 1.1  | Problem in conventional and potential in emerging memories | 3    |

| 2.1  | Memory cell                                                | 9    |

| 2.2  | Classification of memory technology                        | 10   |

| 2.3  | Electrical cell structure of SRAM                          | 12   |

| 2.4  | Electrical cell structure of DRAM                          | 13   |

| 2.5  | Structure of FRAM memorycell                               | 16   |

| 2.6  | Basic MRAM based on pre-charge sense amplifier             | 18   |

| 2.7  | Schematic cross-section of PCRAM cell                      | 20   |

| 2.8  | Electrical cell structure of ReRAM                         | 22   |

| 2.9  | Memory cell structure of ORAM                              | 23   |

| 2.10 | ReRAM structure                                            | 28   |

| 2.11 | Potentials of ReRAM                                        | 29   |

| 2.12 | Challenges of ReRAM                                        | 29   |

| 2.13 | Abstraction levels of memory model                         | 32   |

| 2.14 | Published functional diagram of ReRAM                      | 34   |

| 2.15 | The I-V curve for memristor                                | 35   |

| 2.16 | Memristor                                                  | 36   |

| 2.17 | Changes in memristance due to voltage versus time                    | 37 |

|------|----------------------------------------------------------------------|----|

| 2.18 | Possible open defects in ReRAM memory cells                          | 43 |

| 2.19 | Possible bridge defects in ReRAM memory cells                        | 44 |

| 2.20 | Key terminologies related to testing                                 | 45 |

| 2.21 | The manufacturing flow for memory production                         | 49 |

| 2.22 | Classification of memory testing                                     | 50 |

| 3.1  | Flowchart of the research                                            | 58 |

| 3.2  | Workflow for memristor optimization                                  | 59 |

| 3.3  | Steps for the implementation of the SPICE memristor model in Silvaco | 60 |

|      | EDA simulation tools                                                 |    |

| 3.4  | SPICE code of the Joglekar's memristor model                         | 61 |

| 3.5  | SPICE code of the Prodromakis's memristor model                      | 62 |

| 3.6  | SPICE code of the Biolek's memristor model                           | 62 |

| 3.7  | Setup of the simulation                                              | 63 |

| 3.8  | Workflow for development of ReRAM electrical model                   | 65 |

| 3.9  | Signal voltages and timing diagram for ReRAM operation               | 68 |

| 3.10 | Spice commands                                                       | 70 |

| 3.11 | 22nm CMOS logic levels                                               | 71 |

| 3.12 | Workflow for development of faulty ReRAM electrical model            | 72 |

| 3.13 | Location for bridge defects in simulations                           | 75 |

| 3.14 | Workflow for development of DfT technique                            | 78 |

| 3.15 | DfT circuitry                                                        | 79 |

| 4.1  | Simulation circuit for Joglekar's memristor model                    | 84 |

| 4.2  | Simulation results for Joglekar's memristor model                    | 85 |

| 4.3  | Simulation set up and result for Prodromakis's memristor model       | 87 |

| 4.4  | Simulation set up and result for Biolek's memristor model                                     | 88  |

|------|-----------------------------------------------------------------------------------------------|-----|

| 4.5  | The proposed functional block of ReRAM                                                        | 90  |

| 4.6  | 2x2 memory array of ReRAM                                                                     | 91  |

| 4.7  | Schematic of row/column decoder                                                               | 92  |

| 4.8  | Schematic or write/read circuit                                                               | 93  |

| 4.9  | Schematic of hybrid SA                                                                        | 94  |

| 4.10 | Modified Sense Amplifier                                                                      | 95  |

| 4.11 | Full view of ReRAM simulation model                                                           | 96  |

| 4.12 | Result of defect-free simulation (Case 1)                                                     | 97  |

| 4.13 | Result of defect-free simulation (Case 2)                                                     | 98  |

| 4.14 | Simulation results during BW injection                                                        | 100 |

| 4.15 | Logical state for aggressor cell and victim cell (BW injection)                               | 102 |

| 4.16 | Logical state for aggressor cell and victim cell (BB injection)                               | 105 |

| 4.17 | Logical state for aggressor cell and victim cell (BBW injection)                              | 108 |

| 4.18 | Simulation result before and after DfT implementation when $R_{BW}$ =30 $\Omega$              | 111 |

| 4.19 | Output voltage (V <sub>out</sub> ) during bridge injection ( $R_{BW}$ ) and DfT enable        | 112 |

| 4.20 | Simulation result before and after DfT implementation when $R_{BB} = 100\Omega$               | 114 |

| 4.21 | Output voltage ( $V_{out}$ ) during bridge injection ( $R_{BB}$ ) and DfT enable              | 115 |

| 4.22 | Simulation result before and after DfT implementation during                                  | 116 |

|      | $R_{BBW} = 170\Omega$                                                                         |     |

| 4.23 | Output voltage ( $V_{out}$ ) at victim cell during bridge injection ( $R_{BBW}$ ) and         | 118 |

|      | DfT enable                                                                                    |     |

| 4.24 | Output voltage (V <sub>out</sub> ) at adjacent cell during bridge injection ( $R_{BBW}$ ) and | 119 |

|      | DfT enable                                                                                    |     |

### LIST OF ABBREVIATIONS

| RAM   | - | Random Access Memory                    |

|-------|---|-----------------------------------------|

| ReRAM | - | Resistive Random Access Memory          |

| CMOS  | - | Complementary Metal-Oxide Semiconductor |

| GND   | - | Ground                                  |

| DfT   | - | Design-for-Testability                  |

| EDA   | - | Electronic Design Automation            |

| USFs  | - | Undefined State Faults                  |

| SAF   | - | Stuck-at-Faults                         |

| BL    | - | Bitlines                                |

| WL    | - | Wordlines                               |

| NBL   | - | Nano bitlines                           |

| NWL   | - | Nano wordlines                          |

| W/R   | - | Write/read                              |

| wl    | - | Write 1 operation                       |

| w0    | - | Write 0 operation                       |

| rl    | - | Read 1 operation                        |

| r0    | - | Read 0 operation                        |

| SA    | - | Sense Amplifier                         |

| OC    | - | Open in cell                            |

| OW    | - | Open in wordlines                       |

| OB    | - | Open in bitlines                        |

| BB    | - | Bridge between NBLs                     |

| BW    | - | Bridge between NWLs                     |

| BBW   | - | Bridge between NBLs and NWLs            |

| ASRV  | - | Adaptive Sensing Read Voltage           |

| LWV   | - | Low Write Voltage                       |

|       |   |                                         |

### LIST OF PUBLICATIONS

- Arshad, N., Salehuddin, F., Salim, S. I. and Soin, N., 2015. Defect-oriented Test and Design-for-Testability Technique for Resistive Random Access Memory. *Journal of Telecommunication, Electronic and Computer Engineering (JTEC)*, will be published in vol 8. (Scopus)

- Arshad, N., Haron, N.Z. and Salehuddin, F., 2014. Resistive Bridge Fault Simulation and Analysis for Resistive RAM. In *Malaysian Technical Universities Conference on Engineering & Technology (MUCET 2014)*.

pp. 1 – 5. (Scopus)

- Arshad, N., Haron, N.Z, Salehuddin, F, and Soin, N., 2014. Development of Resistive RAM Simulation Model for Defect Analysis and Testing. *Advanced Science Letters*, 20(10-12), pp.1745–1750. (*Proceedings Scopus*)

- Haron, N.Z., Arshad, N. and Salehuddin, F., 2014. Performance Analysis of Memristor Models for RRAM Cell Array Design using SILVACO EDA. Jurnal Teknologi, 3(68), pp.1–6. (Scopus)

- Haron, N.Z., Salehuddin, F., Arshad, N and Zakaria, Z., 2013. A New Test Scheme for Process Variation-Induced Faults in Resistive RAM. Australian Journal of Basic and Applied Sciences, 7(13), pp.43–50. (*Predatory journal*)

Haron, N.Z., Arshad, N., and Herman, S.H., 2013. Detecting Resistive-Opens in RRAM using Programmable DfT Scheme. In 5th Asia Symposium on Quality Electronic Design. pp. 22–26. (Proceedings Scopus)

### **CHAPTER 1**

#### **INTRODUCTION**

### 1.1 Research Background

Nowadays, almost all electronic systems use memories for data storage. The speed of the changing technology that has led to existing of several emerging memory technologies in replacing conventional semiconductor memories, such as Static Random Access Memory (RAM), Dynamic RAM, and Flash, in future computer and embedded systems. The emerging memory technologies such as ferroelectric RAM (FRAM), magnetic RAM (MRAM), spin-torque transfer RAM (STTRAM), phase-change RAM (PCRAM), resistive RAM (ReRAM), and organic RAM (ORAM) (Chung et al. 2010).

In addition, Chung *et al.* (2010) identified that ReRAM has the densest data storage, non-volatility, and fast data access features. Compared to the conventional semiconductor memories and other emerging memory technologies, ReRAM cells can be fabricated without access transistors. Moreover, Crossbar Inc. (Anonymous, 2014) mentioned that the simple structure enables ReRAM to be integrated in crossbar arrays and stacked in multiple layers to form three-dimension (3D) memories. With such novel devices and advanced circuit architecture, ReRAM offers attractive potentials, such as an enormous storage capacity, low power consumption, and simple fabrication, for memory cell array. In fact, the academic researchers at UC Santa Barbara (Lastras-Montano *et al.*, 2015), Imperial College (Vallace, 2012), and TU Delft (Zaidi, 2012) have been intensively studying this emerging memory. On top of that, semiconductor

companies, such as Hewlett-Packard (HP) at USA, Crossbar Inc. in California, Hynix in South Africa, and Interuniversity Microelectronics Centre (IMEC) in Belgium, have been expected to market ReRAM as a product in the next few years.

### **1.2 Problem Statement**

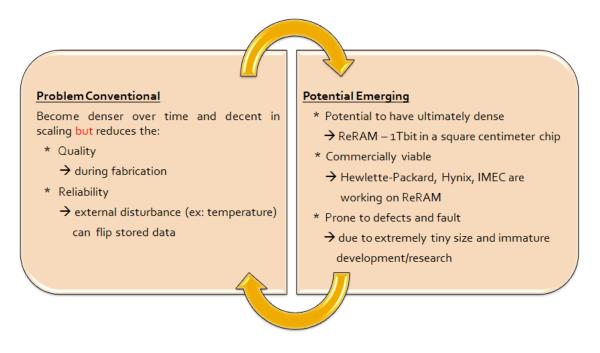

Based on Moore's Law, the number of transistors in a chip was roughly become double per two years. As a result of this downscaling of complementary metal-oxide semiconductor (CMOS) transistor technology, Haron *et al.* (2007) mentioned that CMOS was prone to have several challenges that include physical, material, powerthermal, technological, and economic challenges. Hence, the quality and the reliability of CMOS memories were affected. Figure 1.1 displayed some problems that have been found in conventional memory technologies that have paved way to the existence of the emerging memory technologies. Besides, it cannot be denied that based on Moore's Law, conventional memories have become denser and downscaling overtime, but their quality and reliability have been affected due to the rapid changes of technology development.

Figure 1.1 also reflected the relationship between the conventional memory technology and the emerging memory technology, where the problems inherent in the conventional memory technology have led to the existence of the emerging memory technology like ReRAM. Thus, it is believed that the target memory, ReRAM, is expected to suffer from quality problems. In general, these problems arise due to the size of the components used to form the memory, which was very tiny and closely structured. At the same time, fabricating such tiny and dense structure requires very precise and mature fabrication techniques. Furthermore, the fundamental operation and the types of memristors used as ReRAM cells have not been fully understood and are

2

still debatable. Moreover, in the perspective of quality improvement of ReRAM, very limited work has been published so far. Apart from that, understanding the faulty behavior of the memory devices in the presence of defects enables the development of appropriate faulty models and efficient test schemes; thus, improve the quality of outgoing product.

Figure 1.1: Problems in conventional and potential in emerging memories.

Furthermore, it has been proven by Hamdioui (2001) that fast analysis of quality improvement can be eased by using electrical model. However, ReRAM electrical models are still not reliable as this memory technology is still in infancy stage. Therefore, developing an electrical model for ReRAM had been necessary in this research. This model serves as the starting points for faulty ReRAM electrical model development and quality testing for bridge defect development.

In addition, previous work published by Haron *et al.* (2011) revealed that when ReRAM cells were impacted by resistive open defects (due to insufficient dopant), the write operation might fail. For example, writing logic 1 to an impacted ReRAM cell that stores logic 0 will set the cell to an undefined state; when a read operation is performed to this faulty cell, an arbitrary logic output will be returned. Nevertheless, such faulty behavior is hard to be detected by the existing test schemes, which are based on either logic 1 ( $V_{dd}$ ) or 0 (GND). Therefore, defective ReRAMs might escape the manufacturing test and cause computers, as well as embedded systems installed with such memories, fail to function properly.

### 1.3 **Objectives**

The main goal of this research was to propose a new design-for-Testability (DfT) technique in detecting a unique fault that could occur in faulty ReRAM cell. The following were specific objectives for this research.

- i. To design an electrical model of ReRAM.

- To establish electrical faulty models for bridge defects between ReRAM cells.

- iii. To develop DfT technique to test the bridge defects that had an impact on ReRAM cell.

### **1.4 Scope of Research**

Several limitations of this research need to be acknowledged. This research was conducted by running simulation using a simulation tool known as SILVACO Electronic Design Automation (EDA) software. During the ReRAM modeling stage, the memristor model that was considered for this device only consisted of the memristor SPICE model. In addition, the ReRAM model that was developed had been based on electrical level. The design of memory array for this ReRAM only involved 2x2 array. The 2x2 ReRAM array had been sufficient for this simulation as there was high potential for bridge defects to occur between two adjacent ReRAM cells.

Besides, this research had focused on testing the faulty ReRAM that was induced by bridge defect that occurred in the memory array. During simulation, the data collections for the simulation results concentrated on the values of output voltage that were measured at sense amplifier. Lastly, the most important scope in this research is the proposed DfT technique, which was developed to detect Undefined State Faults (USFs) that occur during bridge injection.

#### **1.5** Contributions

This research is motivated by some potential characteristics and challenges in this emerging memory technology of ReRAM. Hence, it is believed that this research can improve the quality and the reliability of ReRAM. The outcomes of this research are summarized in several contributions, which are ReRAM electrical model, faulty models for bridge defect in ReRAM, and DfT technique for bridge defect in ReRAM.

### 1.5.1 ReRAM Electrical Model

The modeling for ReRAM electrical model had been based on the functional model of memory technology. The optimal memristor model that was published in Jurnal Teknologi publication played an important role in modelling this ReRAM. Furthermore, the simulation of defect-free ReRAM model ensured its functionality. In fact, this modeling was presented in International Conference on Internet Services Technology and Information Engineering (ISTIE 2014) and published in Advanced Science Letters publication.

#### **1.5.2 Faulty Models for Bridge Defect in ReRAM**

The development of the defect-free ReRAM model was adopted to model the faulty models. The faulty models that were comprised of bridge defect had been important for defect analysis and testing. Besides, this work was presented in the Malaysian Technical Universities Conference on Engineering and Technology (MUCET 2014).

#### 1.5.3 DfT Technique for Bridge Defect in ReRAM

The DfT technique was introduced to detect the faulty models. The technique was developed by adopting the idea on how sense amplifier works and the concept of memristor operation. The DfT technique that namely as Adaptive Sensing Read Voltage (ASRV) technique could be applied for off-line and on-line tests at the manufacturing plant in order to improve the product quality and reliability. The proposed DfT technique was accepted for Journal of Telecommunication, Electronic, and Computer Engineering (JTEC) publication.

### 1.6 Thesis Organization

This thesis was organized in five chapters: introduction, literature review, methodology, results and discussion, conclusion and future work. Chapter 1 presented the introductory for understanding the research background. It provided the research background, the problem statement, the objectives, the scope of research, the methodology, and the contributions of this research.

Chapter 2 reviewed the research background of the study. Firstly, it presented a review on memory technologies for memory concept, memory technology classification, conventional memory technologies, and emerging memory technologies.